# **Digital Circuits**

**Electrical & Computer Engineering Department (ECED) Course Notes**

W25121386C

ECED2200

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

# **Table of Contents**

| Digital Circuits             | 7  |

|------------------------------|----|

| Logic Gates                  | 8  |

| AND Gate                     | 8  |

| OR Gate                      | 9  |

| NOT Gate                     | 10 |

| NOR Gate                     | 11 |

| NAND Gates                   | 12 |

| XOR Gate                     | 15 |

| X NOR Gate                   | 16 |

| Additional Gates             | 17 |

| Electric Switches            | 17 |

| Diodes                       | 17 |

| Transistors                  | 19 |

| Logic Classifications        | 21 |

| The Breadboard               | 23 |

| Number Systems               | 25 |

| Binary Numbers               | 25 |

| Number Conversion            | 26 |

| Binary to Decimal Conversion | 26 |

| Decimal to Binary Conversion | 27 |

| Binary Arithmetic            | 28 |

| Binary Addition              | 28 |

| Binary Subtraction           | 30 |

| Binary Multiplication        | 31 |

| Binary Division              | 33 |

|                              |    |

| Bits, Bytes and Words                                         | 35 |

|---------------------------------------------------------------|----|

| Other Notations                                               | 35 |

| Octal Number System                                           | 35 |

| Hexadecimal Numbering System                                  | 37 |

| Signed Magnitudes                                             | 39 |

| Complements                                                   | 40 |

| Two's Complement Arithmetic                                   | 44 |

| Binary Coded Decimal                                          | 47 |

| Boolean Algebra                                               |    |

| Boolean Theorems                                              | 48 |

| Boolean Postulates in 0 and 1                                 | 48 |

| Basic Boolean Identities                                      | 49 |

| De Morgan's Theorems                                          | 51 |

| Logic Circuit Analysis                                        | 52 |

| Two-Level Combinational Logic                                 | 54 |

| Logic Circuit Synthesis                                       | 55 |

| Adding                                                        | 55 |

| The Half Adder                                                | 55 |

| The Full Adder                                                | 58 |

| Subtraction                                                   | 63 |

| Direct Approach                                               | 63 |

| Indirect Approach (Using Adders)                              | 64 |

| Arithmetic Logic Unit (ALU)                                   | 64 |

| A Design Procedure                                            |    |

| Two-Level Canonical Forms                                     |    |

| Sum of Products                                               | 69 |

| Product of Sums                                               | 72 |

| ECED2200 Digital Circuits Notes – © 2012 Dalhousie University |    |

| Conversion Between Canonical Forms                            |     |

|---------------------------------------------------------------|-----|

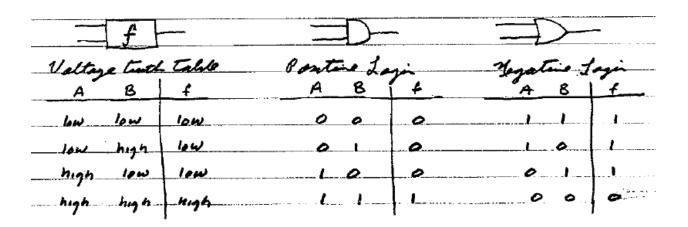

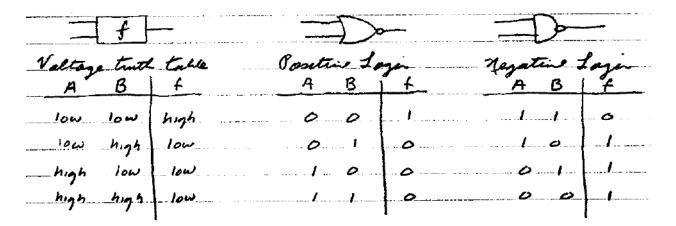

| Positive Versus Negative Logic                                | 74  |

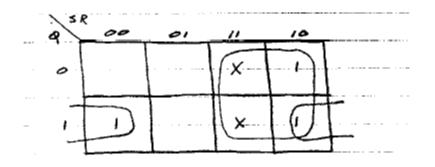

| Minimization by Mapping                                       | 76  |

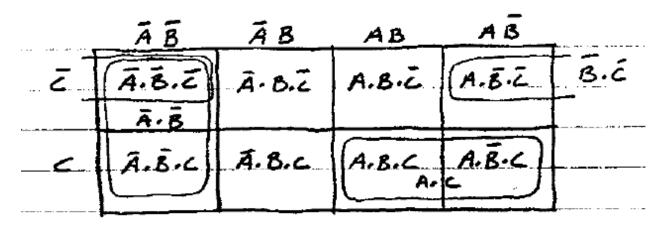

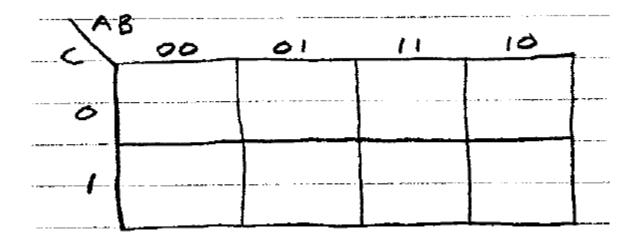

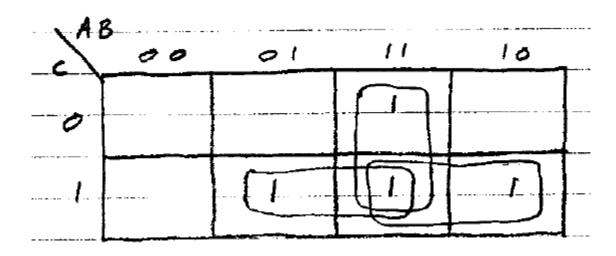

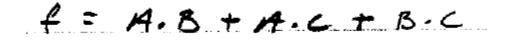

| Karnaugh Maps (K-Maps)                                        | 76  |

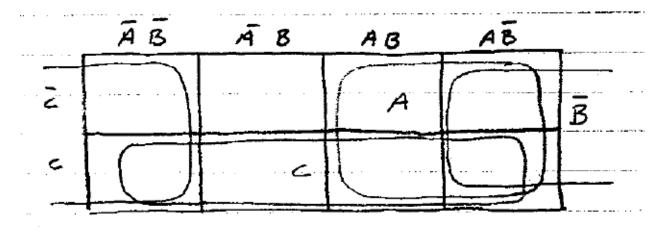

| Mapping in Four Variables                                     | 83  |

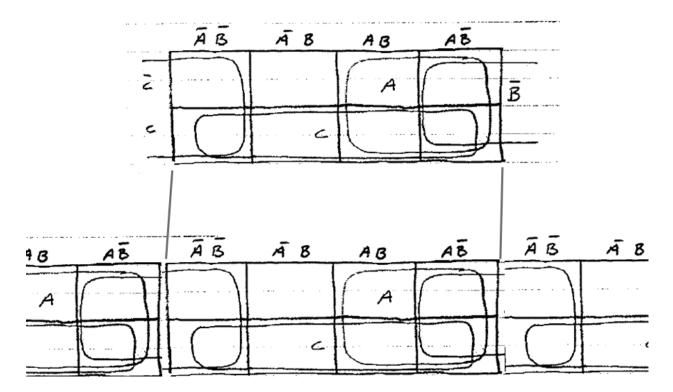

| Five-Variable Maps                                            | 87  |

| Comments on Maps                                              | 89  |

| Some More Notes: Implicants                                   |     |

| Multilevel Combinational Logic                                |     |

| Conversion to NAND and NOR Networks                           |     |

| Computer Aided Design Tools                                   |     |

| Time Response in Combination Networks                         |     |

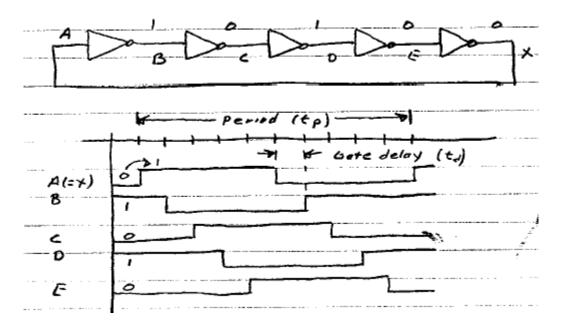

| Gate Delays                                                   | 109 |

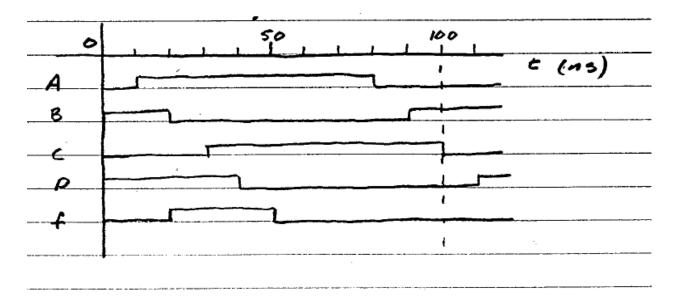

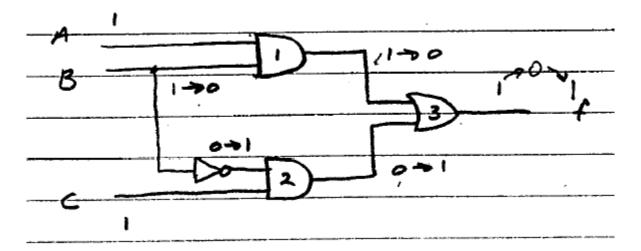

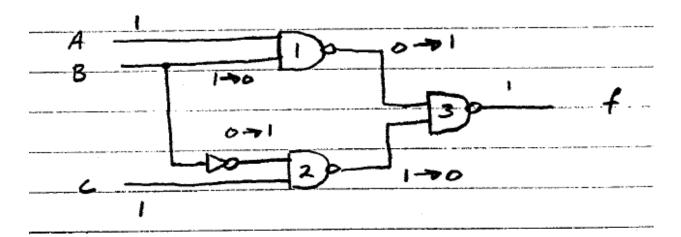

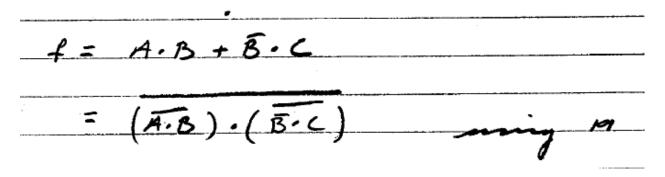

| Timing Waveforms                                              | 109 |

| Hazards and Glitches                                          |     |

| Hazards in Multilevel Networks                                | 115 |

| Programmable and Steering Logic                               |     |

| PAL's and PLA's                                               | 120 |

| The Difference Between PLA's and PAL's                        | 121 |

| Design Procedure                                              | 127 |

| Beyond Simple Logic Gates                                     |     |

| Switching Logic                                               |     |

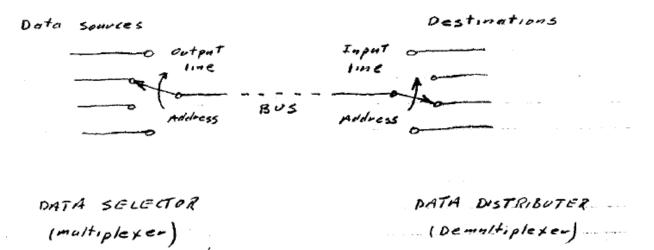

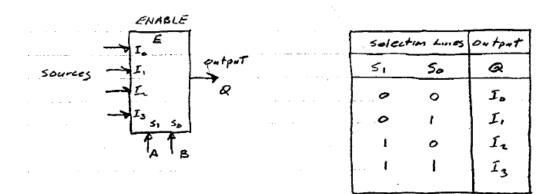

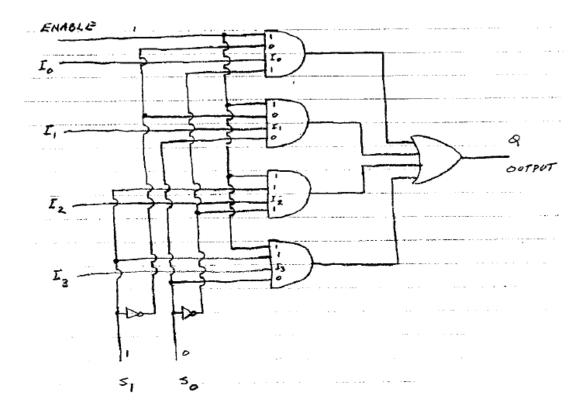

| Multiplexer/Data Selector                                     | 133 |

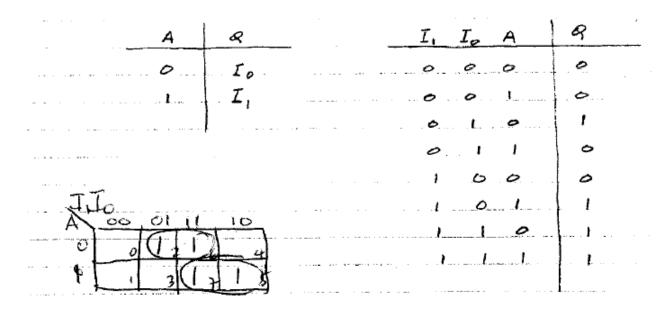

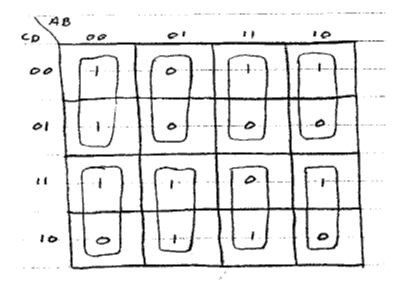

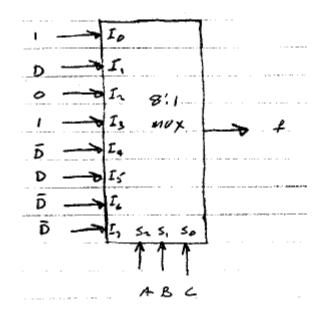

| Multiplexer as a Logic Building Block                         | 137 |

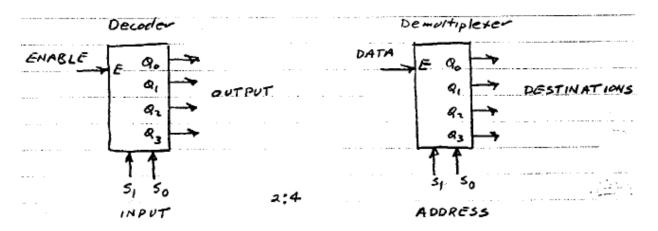

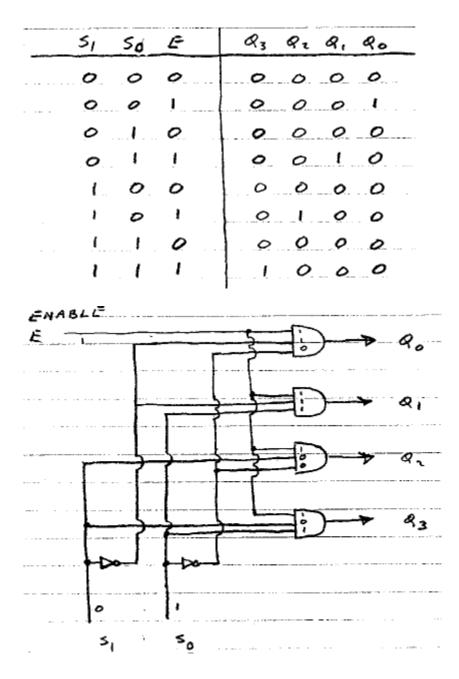

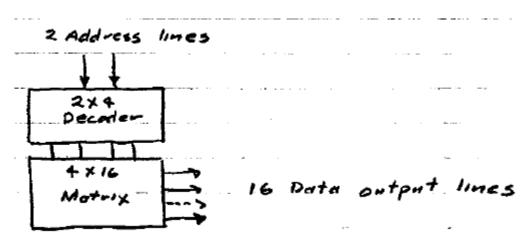

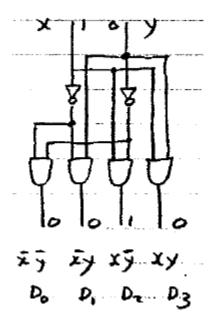

| Decoders/Demultiplexer/Data Distribution                      | 140 |

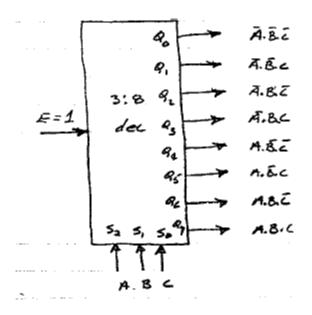

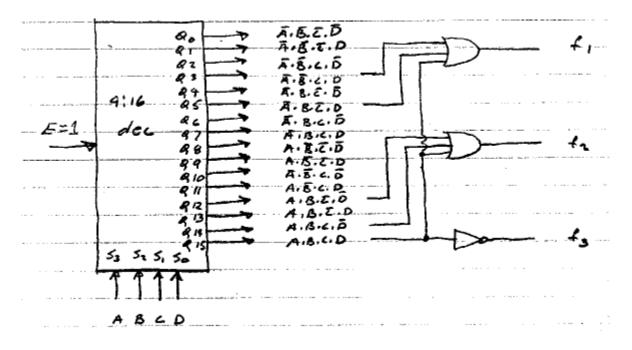

| Decoder/Demultiplexer as a Logic Building Block               | 142 |

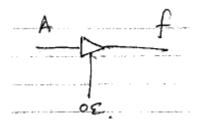

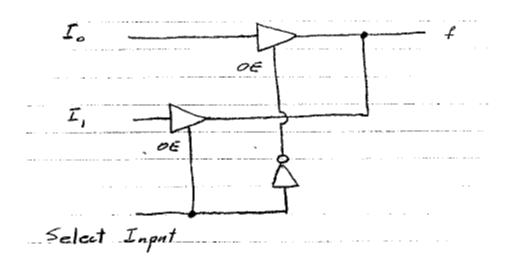

| Tri-State Gates                                               | 145 |

| Sequential Logic Design                                       |     |

| ECED2200 Digital Circuits Notes – © 2012 Dalhousie University |     |

| Logic Gate Memory Units                                                                                                                                                                                                                                                                           | 147                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

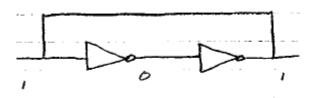

| Inverter Chains                                                                                                                                                                                                                                                                                   | 147                                                         |

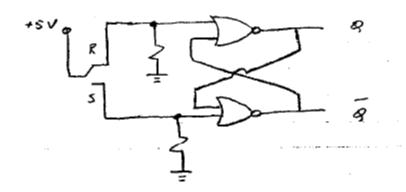

| Cross-Coupled NOR Gates                                                                                                                                                                                                                                                                           | 148                                                         |

| Timing Waveforms                                                                                                                                                                                                                                                                                  | 152                                                         |

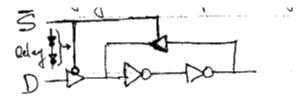

| The Data Latch                                                                                                                                                                                                                                                                                    | 153                                                         |

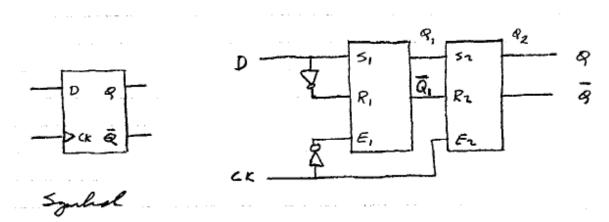

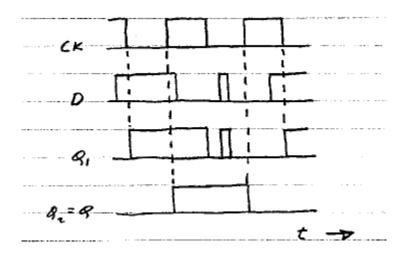

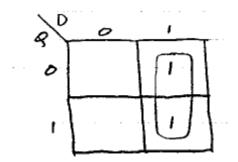

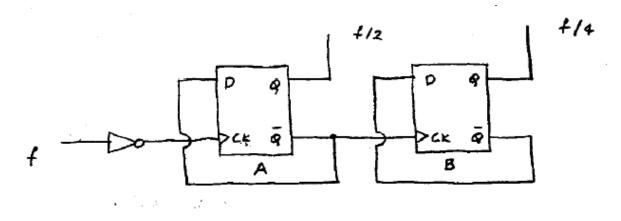

| The D Flip-Flops                                                                                                                                                                                                                                                                                  | 155                                                         |

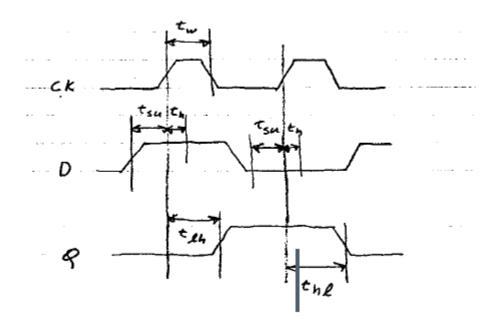

| Timing                                                                                                                                                                                                                                                                                            | 156                                                         |

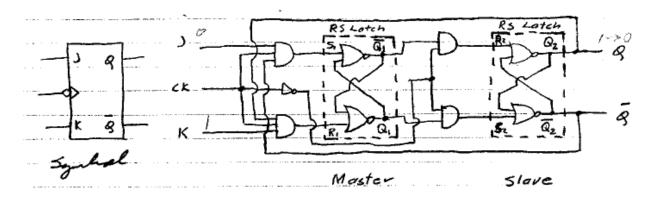

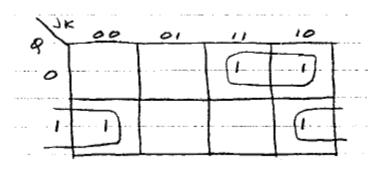

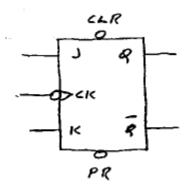

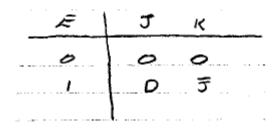

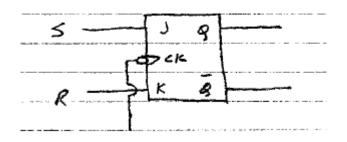

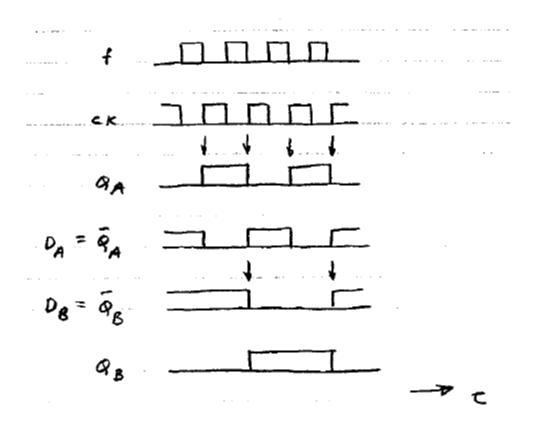

| The JK-Flip Flop                                                                                                                                                                                                                                                                                  | 157                                                         |

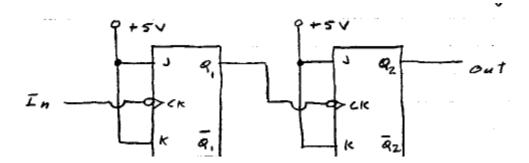

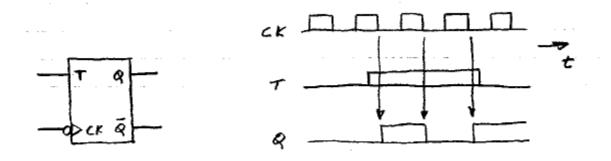

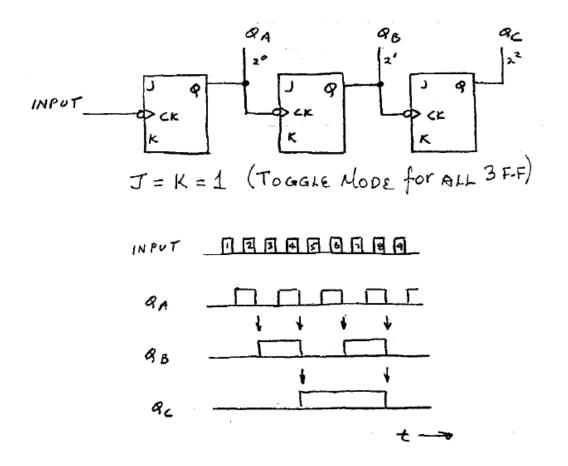

| The T Flip-Flop                                                                                                                                                                                                                                                                                   | 161                                                         |

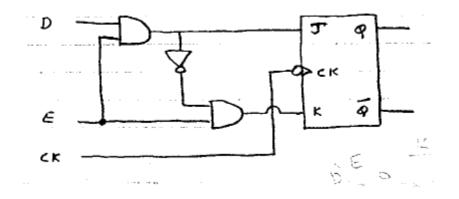

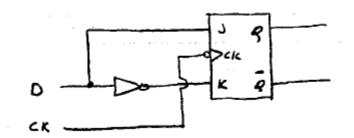

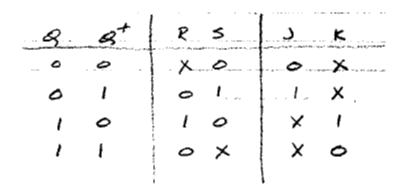

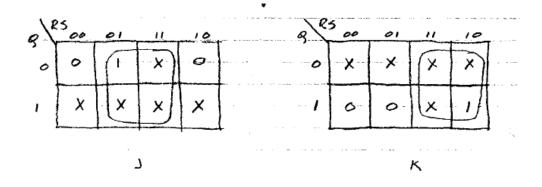

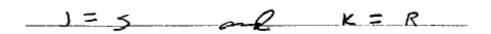

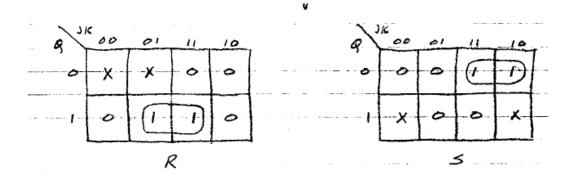

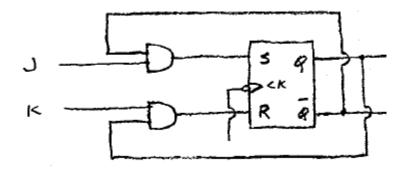

| Conversion of One Flip-Flop Type to Another                                                                                                                                                                                                                                                       | 162                                                         |

| Practical Matters                                                                                                                                                                                                                                                                                 | 168                                                         |

| Debouncing Switches                                                                                                                                                                                                                                                                               | 169                                                         |

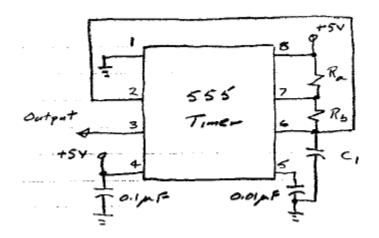

| The 555 Timer                                                                                                                                                                                                                                                                                     | 170                                                         |

|                                                                                                                                                                                                                                                                                                   |                                                             |

| Sequential Logic Applications                                                                                                                                                                                                                                                                     | 172                                                         |

| Sequential Logic Applications                                                                                                                                                                                                                                                                     |                                                             |

|                                                                                                                                                                                                                                                                                                   | 172                                                         |

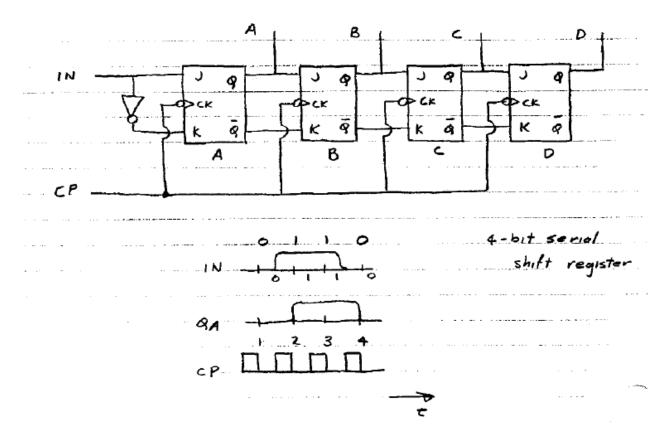

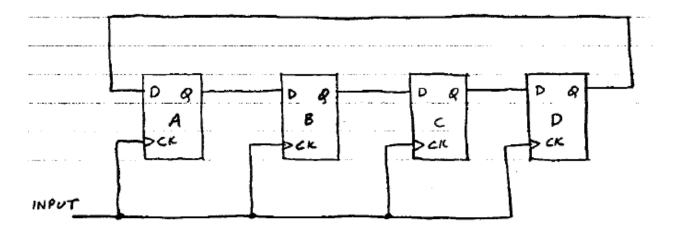

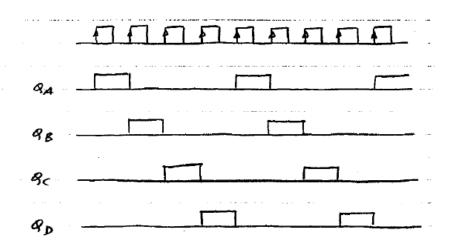

| Registers                                                                                                                                                                                                                                                                                         | 172<br>172                                                  |

| Registers                                                                                                                                                                                                                                                                                         | 172<br>172<br>175                                           |

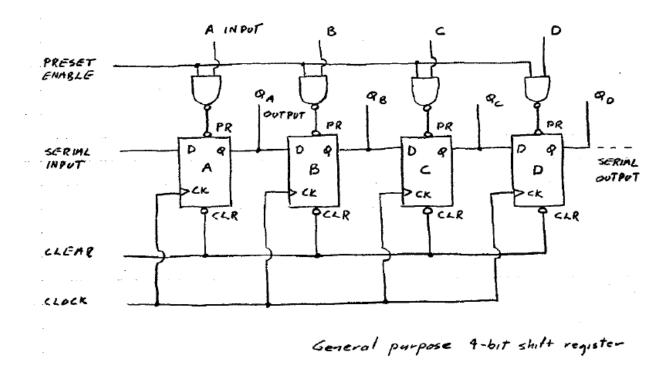

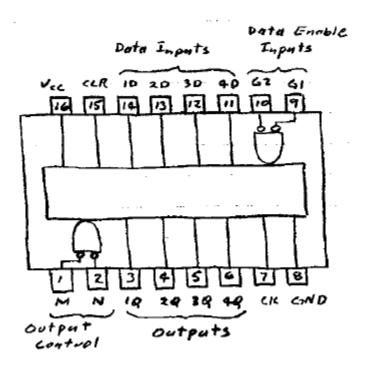

| Registers<br>Shift Registers<br>A Practical Register                                                                                                                                                                                                                                              | 172<br>172<br>175<br>176                                    |

| Registers                                                                                                                                                                                                                                                                                         | 172<br>172<br>175<br>176<br>176                             |

| Registers<br>Shift Registers<br>A Practical Register<br>Counters<br>Types of Counters                                                                                                                                                                                                             | 172<br>172<br>175<br>176<br>176<br>176                      |

| Registers                                                                                                                                                                                                                                                                                         | 172<br>172<br>175<br>176<br>176<br>176                      |

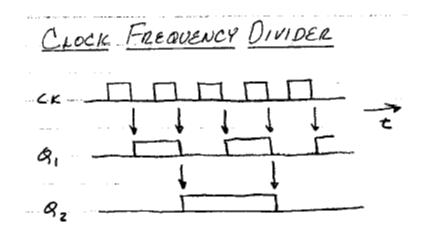

| Registers       2         Shift Registers       2         A Practical Register       2         Counters       2         Types of Counters       2         Divide-by-n Circuits       2         Binary Ripple Counter       2                                                                      | 172<br>172<br>175<br>176<br>176<br>176<br>177<br>180        |

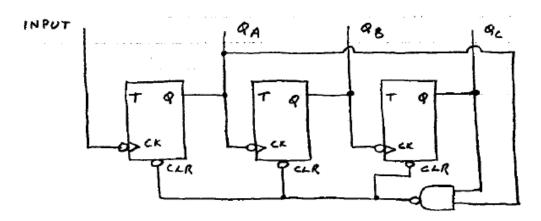

| Registers       Shift Registers         A Practical Register       Sounders         Counters       Sounders         Types of Counters       Sounders         Divide-by-n Circuits       Sounders         Binary Ripple Counter       Sounders         Decade Counters       Sounders              | 172<br>175<br>176<br>176<br>176<br>177<br>180<br>183        |

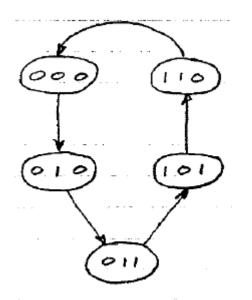

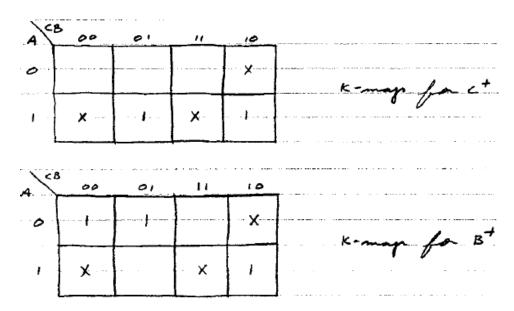

| Registers       2         Shift Registers       2         A Practical Register       2         Counters       2         Types of Counters       2         Divide-by-n Circuits       2         Binary Ripple Counter       2         Decade Counters       2         Synchronous Counters       2 | 172<br>175<br>176<br>176<br>176<br>177<br>180<br>183<br>184 |

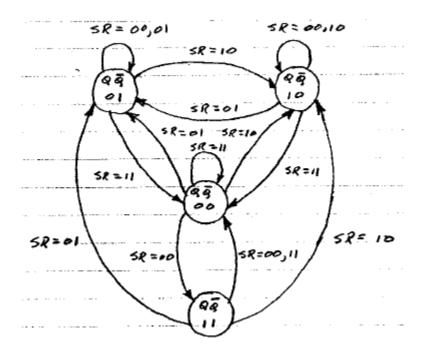

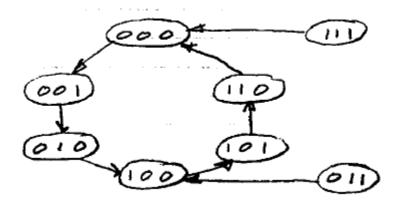

| Verifying if a Counter is Self-Starting1            | .91 |

|-----------------------------------------------------|-----|

| Counter Reset 1                                     | .93 |

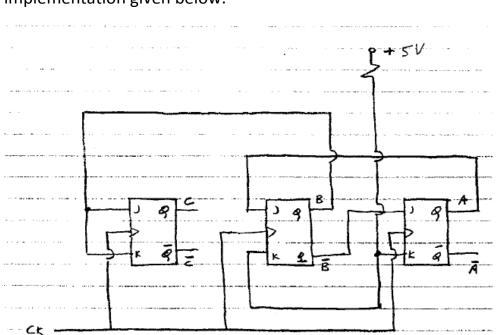

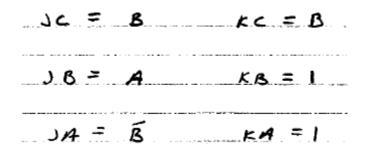

| Implementation with Different Kinds of Flip-Flops1  | .94 |

| Comparison & Summary of Different Implementations 2 | .04 |

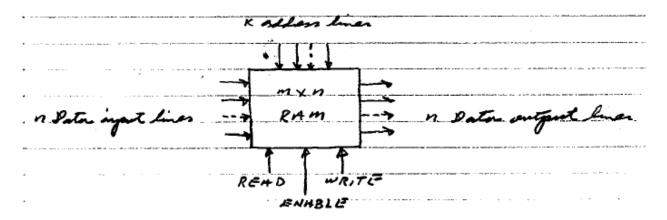

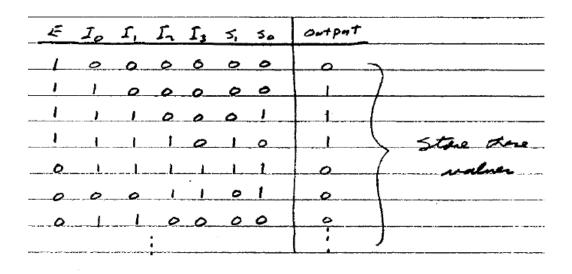

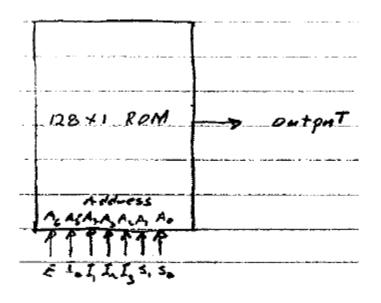

| Memory                                              | 207 |

| RAM 2                                               | .07 |

| ROM 2                                               | 11  |

| Finite State Machines                               | 216 |

| Finite State Machine Design Procedure2              | 16  |

| Moore and Mealy Machines2                           | 27  |

| The Moor Machine 2                                  | 27  |

| The Mealy Machine 2                                 | 29  |

| Alternative State Machine Representations 2         | 36  |

# **Digital Circuits**

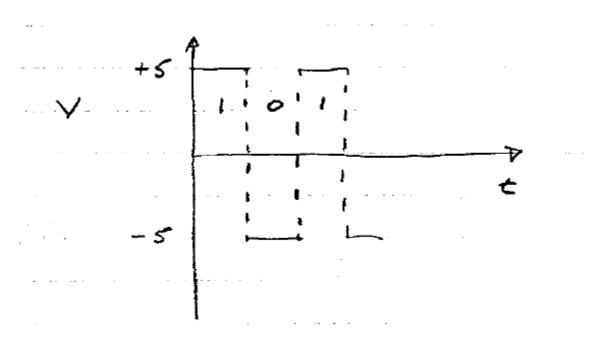

Digital Circuits have inputs and outputs that are represented by discrete values. The figure below shows a typical output for a digital circuit.

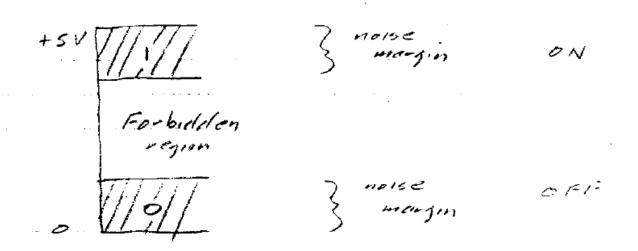

There are two possible output values, namely ±5 volts. Two distinct voltage levels separated by a forbidden region electronically represent the binary numbers 1 and 0.

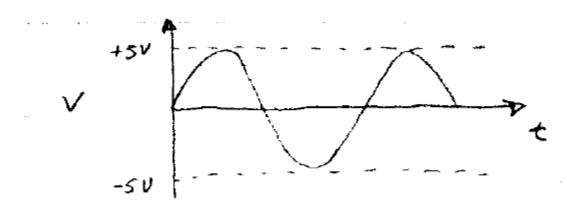

In analog circuits the inputs and outputs have continuous values as show below:

Analog waveform more realistically represent physical quantities such as sound and temperature. Digital waveforms only approximate real values if there are many discrete values. Digital waveforms, however, can best represent degraded signals.

## **Logic Gates**

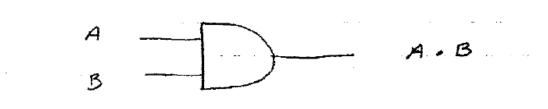

A *gate* is a device that controls the flow of information, usually in the form of pulses. Each logic operation will be indicated by a symbol whose function is defined by a truth table that shows all possible inputs and the corresponding outputs.

## **AND Gate**

<u>Symbol</u>

$A \bullet B$  is read "A and B".

#### **Truth Table**

| <br>A | B | A.B |

|-------|---|-----|

| 0     | 0 | 0   |

| 0     | 1 | 0   |

| 1     | 0 | 0   |

| I     | 1 | 1 1 |

An output appears only when there are inputs at A and B. In general, there may be several input terminals.

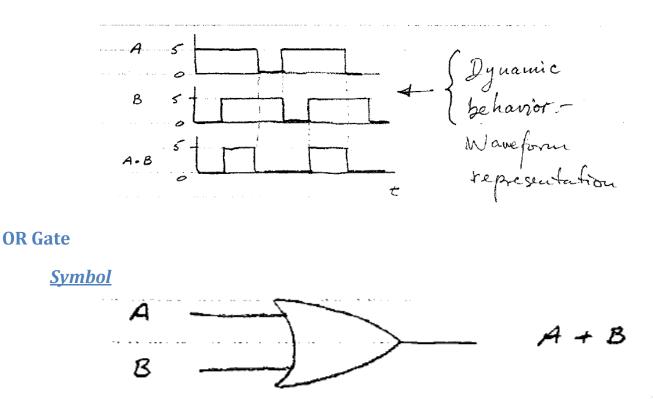

## **Typical Response**

A typical response for two inputs varying with time is shown below:

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

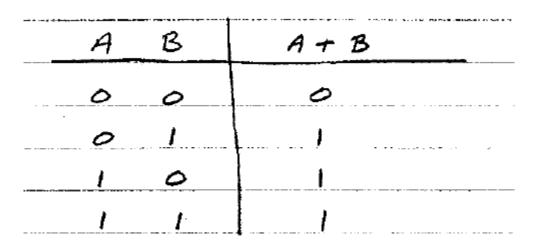

## **Truth Table**

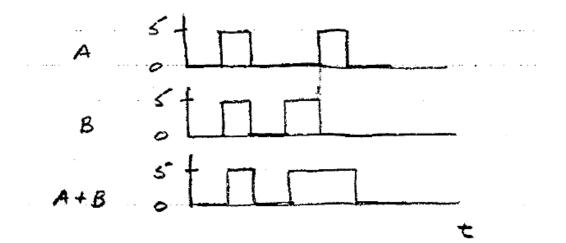

## **Typical Response**

A typical response for two inputs varying with time is shown below:

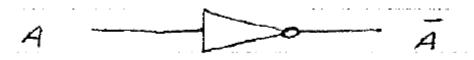

## **NOT Gate**

Signal inversion corresponds to a logic NOT.

## <u>Symbol</u>

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

$\overline{A}$  is read "not A".

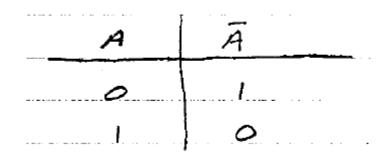

Truth Table

The NOT element is an inverter; the output is the complement of the signal input.

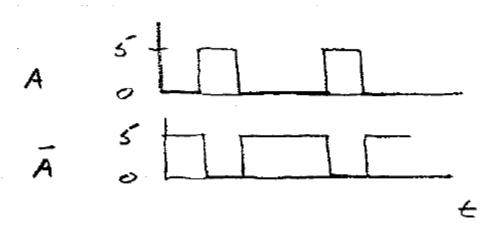

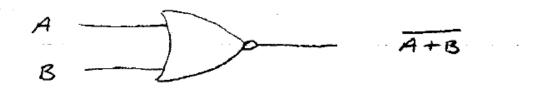

## **NOR Gate**

An inverted OR gate results in a NOT OR or NOR operation.

#### **Symbol**

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

The small circle at the output of the gate, and the line over A + B indicate the inversion process. Thus  $\overline{A+B}$  is A+B inverted.

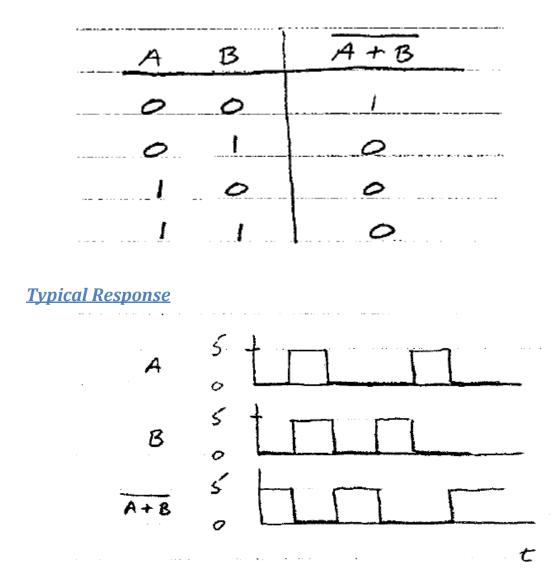

## <u>Truth Table</u>

All basic logic operations can be achieved by using only NOR gates.

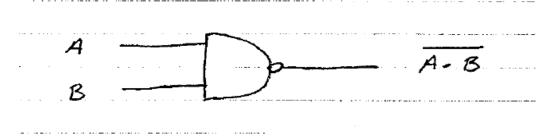

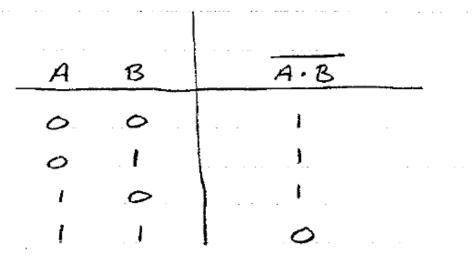

#### **NAND Gates**

An inverted AND gate results in a NOT AND or NAND operation. A NAND gate has all the advantages of a NOR gate and is very easy to fabricate. In a complex logic system, it is convenient to use one type of gate, even when simpler types would be satisfactory, so that gate characteristics are the same for the whole system.

ECED2200 Digital Circuits Notes - © 2012 Dalhousie University

## <u>Symbol</u>

The small circle and the line over A • B indicate inversion.

#### **Truth Table**

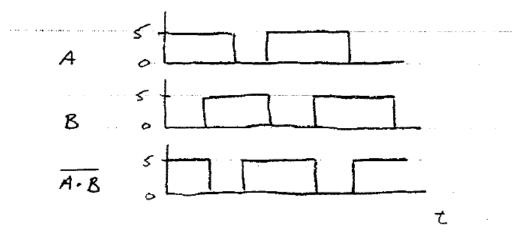

## **Typical Response**

Three NAND gates can be used to replace an OR gate. The combination of NAND gates is equivalent to an OR gate in that it performs the same logic operation (see example below).

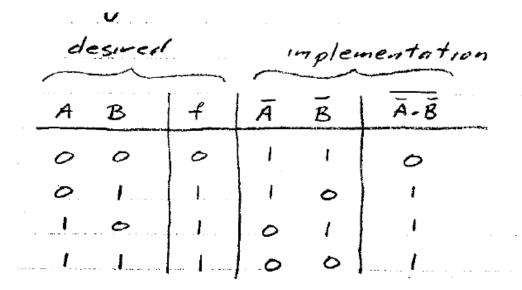

## Example:

Use NAND gates to form a two-input OR gate.

The desired function is defined by the following truth table:

From the table we see that if each input were inverted (replaced by its complement) the NAND gate would produce the desired result as indicated in the table.

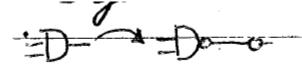

To obtain the inversion, tie both terminals of a NAND gate together as shown below.

In digital notation, the function f is defined by:

$$f = \overline{\overline{A} \bullet \overline{B}} = A + B$$

This relation was obtained by comparing the desired and available truth tables. A "digital algebra" for direct manipulation of such expressions will be considered later.

## **XOR Gate**

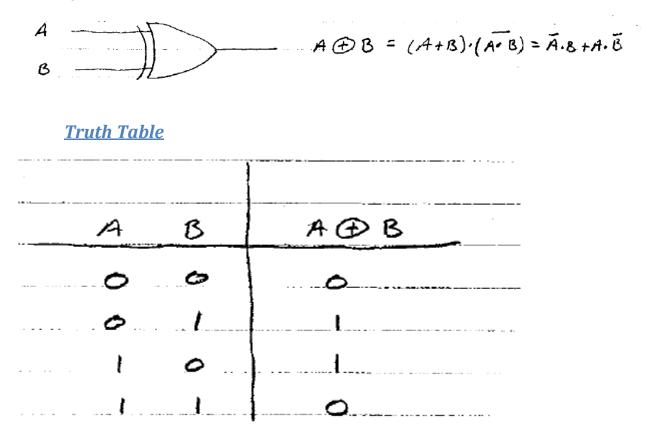

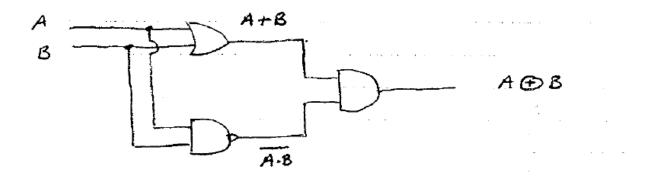

As indicated by the truth tables, the Exclusive-OR operation can be expressed as  $(A+B) \cdot (\overline{A \cdot B})$  which reads "(A or B) and not (A and B)". The alternate form  $\overline{A} \cdot B + A \cdot \overline{B}$  is called an *inequality comparator* since it provides an output of one if A and B are not equal.

<u>Symbol</u>

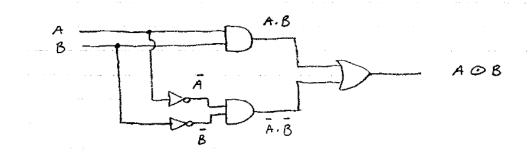

One realization of this gate is shown below:

## **X NOR Gate**

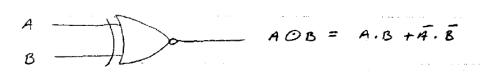

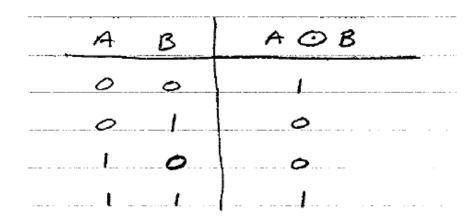

The exclusive-NOR operator can be expressed as (see the truth tables)  $A \cdot B + \overline{A} \cdot \overline{B}$ . It is the inverse of the inequality comparator  $\overline{\overline{A} \cdot B} + \overline{A \cdot B}$ . This is an "equality comparator" since the output is 1 if A and B are equal.

<u>Symbol</u>

**Truth Table**

One realization of this gate is shown below:

## **Additional Gates**

The following truth table shows all possible gates. This is based on writing out all possible variations of the truth table, with names for some of those gates given:

| A  | B | ta | fı. | 11 | f3 | f#       | £        | fc | f 🤈 | fy | 4 | f.o | f,,  | fiz | 43 | +19 | +15 |

|----|---|----|-----|----|----|----------|----------|----|-----|----|---|-----|------|-----|----|-----|-----|

| 0  | 0 | 6  | _0  | 0  | 0  | <i>o</i> | 0        | 0  | 0   |    |   | 1.  | 1    | 1   |    | 1   | 1   |

| 0  | 1 |    | 0   | 0  | 0  |          | <b>]</b> | 1  | 1   | 0  | 0 | 0   | 0    | ļ   | 1  | 1   | 1   |

|    | 0 | 0  | 0   | 1  | 1  | 0        | 0        |    | 1   | 0  | 0 |     |      | 0   | 0  |     | 1   |

| 1  | 1 | 0  |     | 0  | 1  | 0        |          |    |     | 0  | 1 | 0   | 1_   | 0   | 1  | 0   |     |

|    |   |    |     |    |    |          |          |    |     |    |   |     | 14 B |     |    |     |     |

|    |   | •  |     | 1  |    | -        |          |    |     | •  |   |     |      | 1   |    | -   |     |

| 10 |   |    |     |    |    | nati     |          |    |     |    |   |     |      |     |    |     |     |

|    |   |    |     |    |    | (B.A     |          |    |     |    |   |     |      |     |    |     |     |

## **Electric Switches**

## **Diodes**

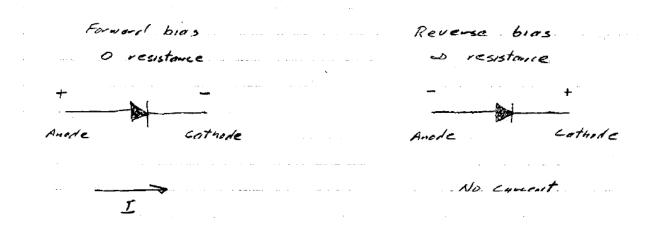

A diode is a two-terminal electrical device that allows current to flow in one direction but not the other. A schematic diagram from a diode is shown below.

If the anode is at a higher voltage than the cathode, the diode is *forward biased*, its resistance is very low, and current flows. The diode has voltage drop of about 0.7V across it. If the anode is at a lower voltage than the cathode, the diode is *reverse biased*, its resistance is very high, and no current flows.

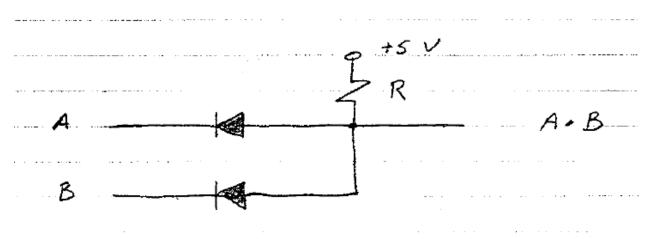

Simple gates can be constructed by using diodes and a resistor. An AND gate is shown below:

If the inputs are positive (> +5V) with respect to ground, inputs at A and B turn off both diodes, no current flows through R and there is a positive output (a 1). In general, there may be several input terminals. If any of those inputs are zero (0), current flows through the forward-biased diode, and the output is nearly zero (0).

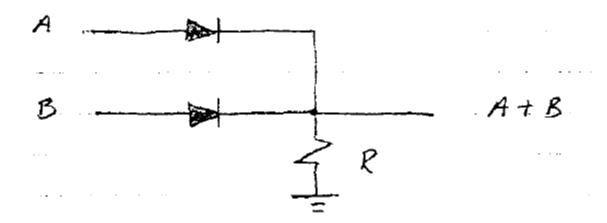

An OR gate is shown below:

For no input (zero voltage) no current flows and the output is zero (0). An input of +5V (1) at either terminal A or B on both (or on any terminal in the general case) forward biases the corresponding diode, current flows through the resistor, and the output voltage rises to nearly 5V (1).

The voltage drop across the diodes add up when circuits of this type are cascaded in series and the voltage levels are degraded. Note that it is not possible to construct and inverter using only diodes and resistors. Transistors can be used to circumvent these problems.

#### **Transistors**

#### <u>Bipolar</u>

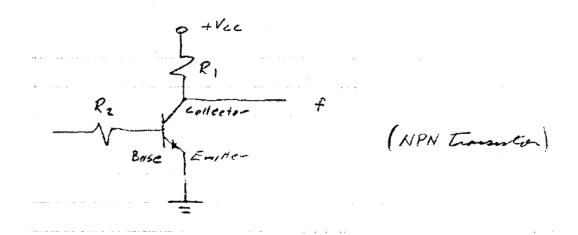

A bipolar transistor is a three-terminal semiconductor device. Under control of one of the terminals, called the *base*, current can below from the *collector* terminal to the *emitter* terminal.

The basic inverter circuit is shown below.

A high voltage at the base turns on the transistor. The output f is discharged to ground, getting close to 0V (but never quite reaching it). When a low voltage is placed on the base, the transistor is turned off. The output node f voltage approaches the power supply voltage Vcc through the pull-up/load resistor R1.

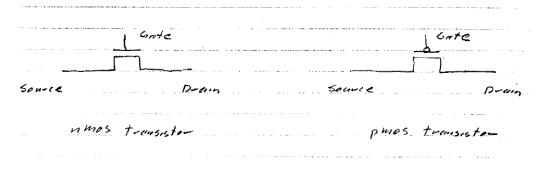

## Metal Oxide Semiconductor

A Metal Oxide Semiconductor (MOS) transistor is a voltagecontrolled switch. It has three terminals: a source, a drain, and a gate. There are two different types of MOS transistors, called nmos and pmos. Their schematic symbols are shown below:

An nmos transistor conducts when a high voltage (1) is placed on its gate, and is non-conducting when a zero voltage (0) is on the gate. The pmos transistor is complementary. A pmos transistor conducts when a logic 0 is placed on the gate, and is non-conducting when a logic 1 is on the gate.

Diodes, transistors, and resistors can be used to implement a wide range of gates.

## **Logic Classifications**

Electronic logic circuits are classified in terms of the components employed. Basic operations can be performed by:

- 1. Diode Logic (DL)

- 2. Resistor-Transistor Logic (RTL)

- 3. Diode-Transistor Logic (DTL)

- 4. Transistor-Transistor Logic (TTL)

- 5. Metal-Oxide Semiconductor (MOS)

- 6. Complementary MOS (CMOS)

- 7. Emitter-Coupled Logic (ECL)

Logic types vary in (a) signal degradation (b) fan-in (c) fan-out and (d) speed.

## <u>Signal Degradation:</u>

As mentioned earlier, a disadvantage of diode logic is that the forward voltage drops is appreciable, and the output signal is degraded. The use of transistors minimizes degradation.

## <u>Fan-In:</u>

The number of inputs that can be accepted is called fin-in. It is low (3 or 4) for DL and high (8 or 10) for TTL.

## <u>Fan-Out:</u>

The number of outputs that can be supplied by a logic element is called the fan-out. Fan-out depends on the output current capacitor (and the input current requirement) and varies from 4 in DL to 10 or more in TTL.

## <u>Speed:</u>

The speed of a logic operation depends on the time required to change the voltage levels, which is determined by the effective time constant of the element. In high speed diodes, the charge storage is so low that response is limited primarily by wiring and lead capacitance. In transistors in the ON stat, base current is high and the charge stored in the base region is high. This charge must be removed before the collector bias can reverse. Typically, 5 to 10 nS are required to process a signal. In ECL, the charge stored is minimal and ECL gates can operate at rates up to 200 MHz.

#### <u>Noise Margin:</u>

The difference between the operating input voltage and the threshold voltage is called the noise margin.

#### TTL Packaged Logic:

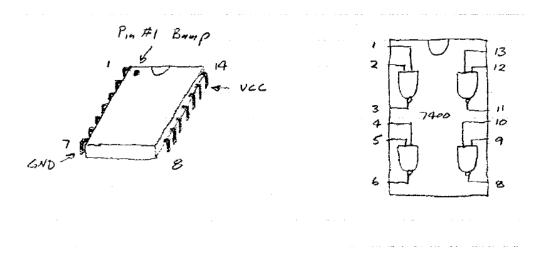

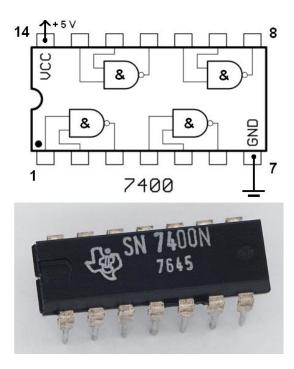

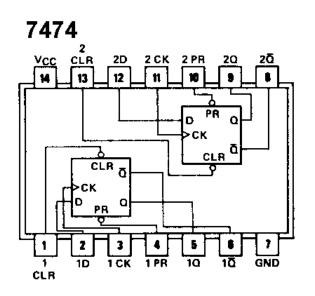

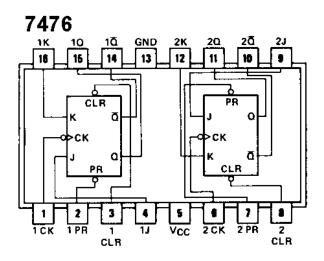

Integrated Circuits containing few than a dozen gates are small-scale integration (SSI); those with more than a hundred elements are large-scaled integration (LSI). In between are medium-scale integration (MSI) circuits. A TTL integrated circuit package typically contains several simple logic gates. The Texas Instruments (TI) 74series components provide the standard number scheme used by the industry. For example, a package containing four 2-input NAND gates is a "7400" while a "7404" contains six inverters. A 14-pin package along with a diagram of its internal logic and pin connectivity is shown below.

Another interpretation:

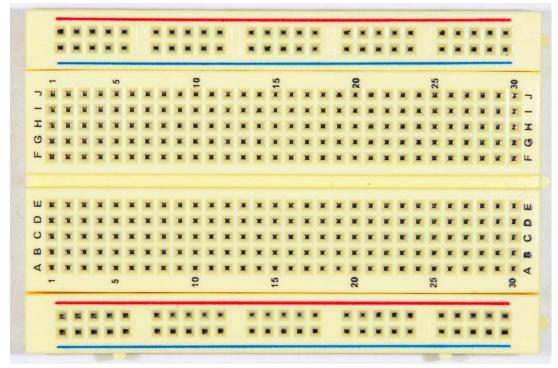

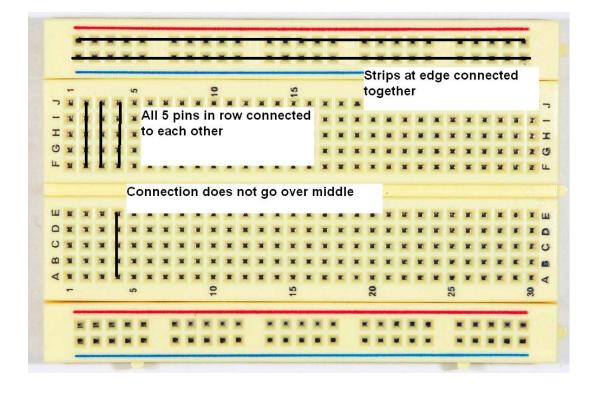

## The Breadboard

## **Number Systems**

To design efficient digital circuits, we need a special numbering system and a special algebra. We will now consider the binary number system and apply logic to binary relations.

## **Binary Numbers**

A number N can be written as a polynomial of the form:

$$N = b_{n-1}r^{n-1} + b_{n-2}r^{n-2} + \dots + b_1r^1 + b_0r^0 + b_{-1}r^{-1} + \dots + b_{-m}r^{-m}$$

$$= \sum_{i=-m}^{n-1} b_ir^i$$

Where:

r = base or radius of the system

$b_i = i^{th} bit (digit)$

b<sub>n-1</sub> = most significant bit (digit) MSB

b<sub>-m</sub> = least significant bit (digit) LSB

n = number of integer bits (digits)

m = number of fraction bits (digits)

and

$$0 \le b_i \le r-1$$

for all i,  $-m \le i \le n-1$

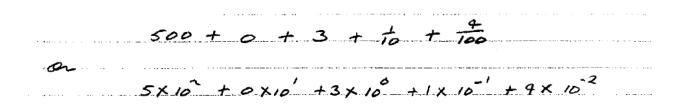

In the decimal system a quantity is represented by the value and the position of a digit. For example, the number 503.14 can be written as:

We see that 10 is the base and each position to the left or right of the decimal point corresponds to a power of 10.

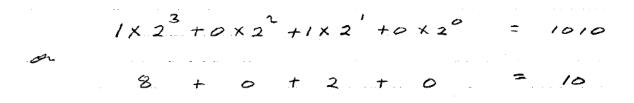

For data with only two possibilities such as the ON-OFF position of a switch which can be represented by the number 0 or 1, we use the binary system. In this system the base is 2. For example the number 10 can be written as:

In electronics 1 and 0 usually correspond to the specified voltage levels e.g.: in TTL, 0 corresponds to a voltage near zero and 1 to a voltage near +5V.

## **Number Conversion**

## **Binary to Decimal Conversion**

In a binary number, each position to the right or left of the "binary point" corresponds to a power of 2, and each power of 2 has a decimal equivalent.

To convert a binary number to its decimal equivalent, add the decimal equivalents of each position occupied by a 1.

## **Example**

Write in decimal the following numbers:

$$\begin{aligned} 110001 &= 1 \times 2^{5} + 1 \times 2^{4} + 0 \times 2^{3} + 0 \times 2^{2} + 0 \times 2^{4} + 1 \times 2^{2} = 32 + 16 + 1 = 49 \\ 101.01 &= 1 \times 2^{2} + 0 \times 2^{4} + 1 \times 2^{0} + 0 \times 2^{-4} + 1 \times 2^{-2} = 4 + 1 + \frac{1}{4} = 5.25 \\ 01011 &= 0 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{4} + 1 \times 2^{0} = 8 + 2 + 1 = 11 \\ 0.0011 &= 0 \times 2^{0} + 0 \times 2^{-4} + 0 \times 2^{-2} + 1 \times 2^{-3} + 1 \times 2^{-4} = \frac{1}{2^{3}} + \frac{1}{2^{4}} = \frac{1}{8} + \frac{1}{16} = 0.1875 \end{aligned}$$

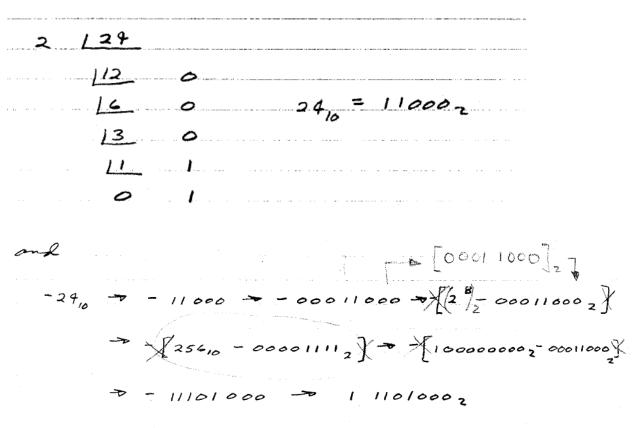

## **Decimal to Binary Conversion**

A decimal number can be converted to its binary equivalent by expressing the decimal number as a sum of powers of 2. A more convenient method is the double-dabble method of handling integers and decimals separately.

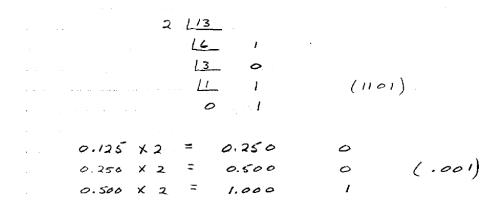

To convert a decimal integer to its binary equivalent, progressively divide the decimal number by 2, noting the remainders; the remainder taken in reverse order forms the binary equivalent.

To convert a decimal fraction to its binary equivalent, progressively multiply the fraction by 2, removing and noting the carries; the carries taken in forward order from the binary equivalent.

## **Example**

Convert decimal 28.375 and 0.625 to their binary equivalent.

A) Using the shorthand notation for the double-dabble method:

The binary equivalent is 11100.

Then convert the fraction:

ECED2200 Digital Circuits Notes - © 2012 Dalhousie University

$$\begin{array}{c} comp \\ 0.375 \times 2 = 0.75 \quad 0 \quad (M58) \\ 0.75 \times 2 = 1.50 \quad 1 \quad contine \ on til \\ 0.50 \times 2 = 1.00 \quad 1 \quad (L58) \quad te \ fraction \ in \\ stop \qquad gene \ on \ te \ down \\ muche \ of \ lite \\ in \ reached \ . \end{array}$$

The binary equivalent is .011

Hence, 28.375 is equivalent to binary 11100.011:

| В)  |       |     |   |       |   |  |

|-----|-------|-----|---|-------|---|--|

| (5) |       |     |   | 1,250 | 1 |  |

| ·   | 0.250 | x 2 |   | 0,500 | 0 |  |

|     | 0.500 | ×2  | = | 1.000 |   |  |

| .,  |       |     |   |       |   |  |

The binary equivalent is 0.101.

## **Binary Arithmetic**

## **Binary Addition**

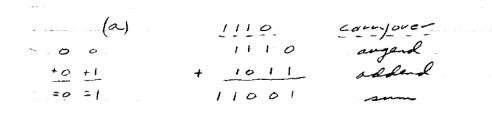

Add column by column carrying where necessary into higher position columns.

**Examples**

A) Perform 1110 + 1011

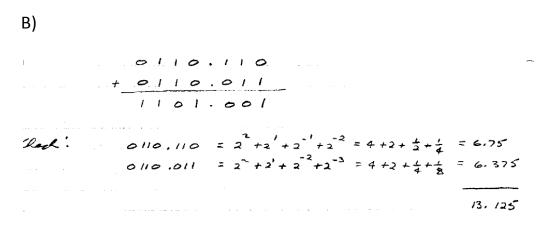

B) Perform 0110.110 + 0110.011

**Results:**

A)

28

## Check your results:

| Chech:   |          |           | 3 2<br>+2 +2 | , | 8+4+2 = | 14 |

|----------|----------|-----------|--------------|---|---------|----|

| <u> </u> |          |           |              |   | 8+2+1 = | 11 |

| 0 +1     |          |           |              |   |         | 25 |

| 1 =10    |          |           |              |   |         |    |

| Corrover | 2 12     | 5         |              |   |         |    |

| ,<br>    | <u>L</u> | 12        | 1            |   |         |    |

| ·····    |          | 6         |              |   |         |    |

|          | L        | 3         | 0            |   |         |    |

| ·        |          | <u>Li</u> | 1            |   |         |    |

|          |          | 0         |              |   |         |    |

#### The binary equivalent is 11001 which checks OK.

The binary equivalent is:

1101.001 is the binary equivalent of 13.125, which checks OK.

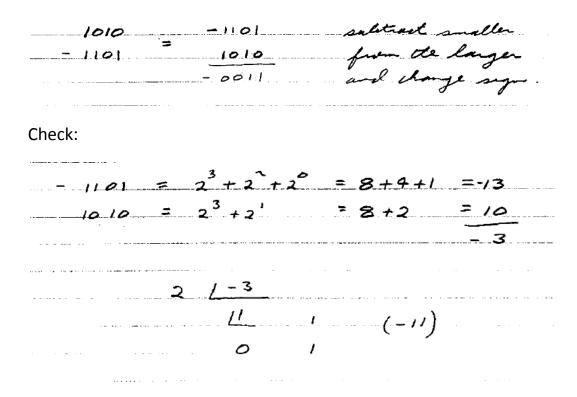

#### **Binary Subtraction**

Subtract column by column borrowing where necessary from higher position columns.

#### **Example:**

Perform the following binary subtractions:

- A) 1101.011 101.101

- B) 1010 1101

Answers:

A)

0010 100 1101.011 meneral 1010.101 subtrahent 0010.110 slifference

Check:

$$1101.011 = 2^{3} + 2^{2} + 2^{2} + 2^{3} = 8 + 9 + 1 + \frac{1}{4} + \frac{1}{8} = 13.375^{-1}$$

$$= 1010.101 = 2^{3} + 2^{1} + 2^{-3} = 8 + 2 + \frac{1}{4} + \frac{1}{8} = -10.625^{-1}$$

$$= 2.750$$

$$2 | 2$$

$$= 1^{1} \qquad (10)$$

$$= 0 \qquad 1 \qquad (10)$$

Hence 10.110 is the binary equivalent to 2.75, so this answer checks out OK.

B)

Hence, -11 is the binary equivalent of -3, so the answer checks out.

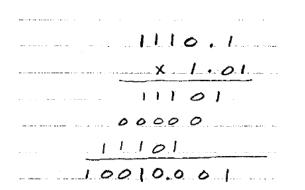

## **Binary Multiplication**

Obtain partial products using the binary multiplication table:

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

0 x 0 = 0 0 x 1 = 0 1 x 0 = 0 1 x 1 = 1

and then add the partial products. The binary point is handled in the same way a decimal point would be when multiplying.

#### **Example**

Perform the following binary multiplication: 1110.1 x 1.01. Check by converting from binary to decimal and multiplying.

Check:

$1110.1 = 2^{3} + 2^{2} + 2^{2} + 2^{2} = 8 + 4 + 2 + \frac{1}{2} = 14.5$  $1.01 = 2^{\circ} + 2^{-2} = 1 + \frac{1}{4} = 1.25$

$$\begin{array}{rcrcrcrcr}

14.5 \\

& 1.25 \\

\hline

725 \\

290 \\

145 \\

\hline

18.125 \\

2 & 18 \\

\hline

19.125 \\

2 & 18 \\

\hline

19 & 0 \\

\hline

14 & 1 \\

\hline

12 & 0 \\

\hline

14 & 0 \\

\hline

14 & 1 \\

\hline

12 & 0 \\

\hline

10010 \\

\hline

11 & 0 \\

\hline

0 & 1 \\

\hline

0.125 & x_2 &= 0.250 \\

0.250 & x_2 &= 0.500 \\

\hline

0.500 & x_2 &= 1.000 \\

\end{array}$$

This shows that 10010.001 is the binary equivalent of 18.125, so the multiplication checks OK.

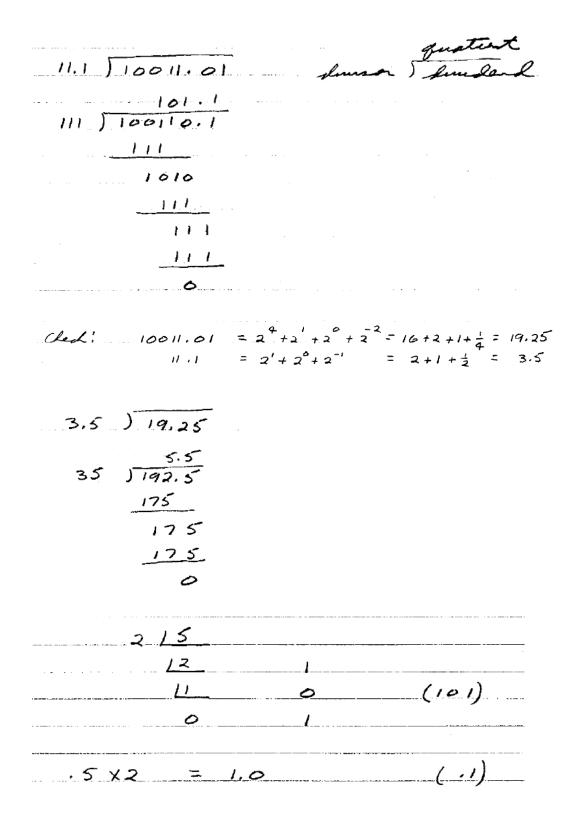

## **Binary Division**

Perform repeated subtractions as in long division of decimals.

#### **Example**

Perform the following binary division:  $10011.01 \div 11.1$ . Check by converting from binary to decimal and then dividing.

Hence, 101.1 is the binary equivalent of 5.5, which checks out OK.

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

## **Bits, Bytes and Words**

A single binary digit is called a "bit". All information in a digital system is represented by a bit.

4 bit sequence is a *nibble*

8 bit sequence is a byte

16 bit sequence is a word

The number of bits in the data sequence processed by a computer is an important characteristic. An 8 bit microprocessor can receive, store, and transmit data or instructions in the form of bytes. Eight bits can be arranged in  $2^8 = 256$  different combinations, thus a byte can have 256 values.

## **Other Notations**

The number of years in a century can be written as 100D or  $100_{10}$  in the decimal system. In binary notation this would be written 01100100B or  $01100100_2$ ; the suffix B or subscript 2 is used wherever necessary to avoid confusion.

## **Octal Number System**

The *octal* number system is a base 8 system and so has eight distinct digits {0, 1, 2, 3, 4, 5, 6, 7 }. It is expressed as a string of any combination of the eight digits. To convert from octal to decimal, we follow the same procedure for converting from binary to decimal; that is, express the octal number in its polynomial form and evaluate this polynomial by using decimal-system addition.

## **Example**

Convert the number 367.2408 to its decimal equivalent.

$$367.240_{g} = 3 \times 8^{2} + 6 \times 8' + 7 \times 8^{2} + 2 \times 8^{2} + 4 \times 8^{2} + 0 \times 8^{-3}$$

$$= 192 + 48 + 7 + \frac{2}{8} + \frac{4}{64} + 0$$

$$= 247 + \frac{20}{64}$$

$$= 247 \cdot 3/25_{10}$$

To convert from decimal to octal we use the same procedure as converting from decimal to binary, but instead of diving by 2 for the integer part, divide by 8 to obtain the octal equivalent. Also, instead of multiplying by 2 for the fractional part, multiply by 8 to obtain the fractional octal equivalent of the decimal system. However, it is more common to convert from binary to octal and vice-versa.

The conversion from binary to octal is accomplished by grouping the binary numbers into groups of 3 bits each, starting from the binary point and proceeding to the right and to the left. Each group is then replaced by its octal equivalent.

**Example**

Convert 01100100<sub>2</sub> into its octal equivalent.

Grouping the bits into groups of 3 bits from the binary point we get:

001 100 100

Note that a leading zero was added to complete the first group. Each group is now replaced by its octal equivalent to get:

001 100 100

1 4 4

Thus,

The three-bit octal numbers are easier to work with than their 8-bit binary equivalents.

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

To convert from octal to binary replace each octal digital by its 3-bit binary equivalent.

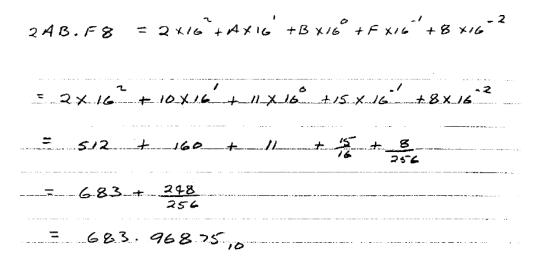

#### Hexadecimal Numbering System

The hexadecimal numbering system is a base-16 system and has sixteen distinct digits {0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F} where A is the equivalent of decimal 10, B to 11, ..., and F to 15. A hexadecimal number is expressed as a string of any combination of the 16 symbols. To convert from hexadecimal to decimal and vice versa we follow the same procedure for conversion between decimal and octal, except we now use 16 instead of 8.

#### **Example**

Convert the number 2AB.F8<sub>16</sub> to its decimal equivalent.

To convert from binary to hexadecimal group the binary numbers into 4 bits each; starting from the binary point and proceeding to the right and to the left and then replace each group by its hexadecimal equivalent.

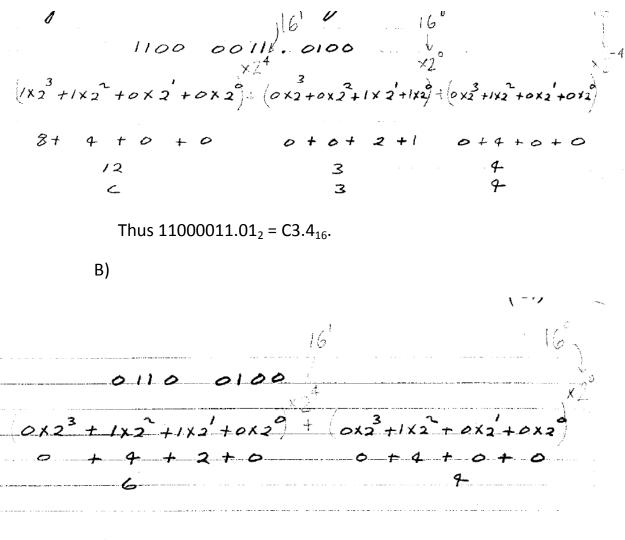

#### **Example**

Convert the following into their hexadecimal equivalents.

- A)  $11000011.01_2$

- B) 01100100<sub>2</sub>

**Results:**

ECED2200 Digital Circuits Notes - © 2012 Dalhousie University

A) Group the bits into groups of 4 bits from the binary point and replace each group by its hexadecimal equivalent:

Thus  $01100100_2 = 64H = 64_{16}$ .

To convert from hexadecimal to binary replace each hexadecimal digit by its 4-bit binary equivalent. A table of the four number systems is given below:

| Decimal | Binary | octal | Hexadecimal |

|---------|--------|-------|-------------|

| 0       | 0000   | 00    | 0           |

| 1       | 0001   |       | 1           |

| 2       | 0010   | 02    | 2           |

| 3       | 0011   |       |             |

| <b></b> | 0100   | 04    | 4           |

| 5       | 0101   | 05    | 5           |

| 6       | 0110   | 06    | 6           |

| 7       | 0111   | 07    | 7           |

| 8       | 1000   | 10    |             |

| 9       | 1001   |       | 9           |

| 10      | 1010   | 12    | A           |

| 11      | 1011   | 13    | B           |

| 12      | 11.00  | 14    | C           |

| 13      | 1101   | 15    | Q           |

| . 14    | .1110  | 16    | Ē           |

| 15      | 1///   | 17    | F           |

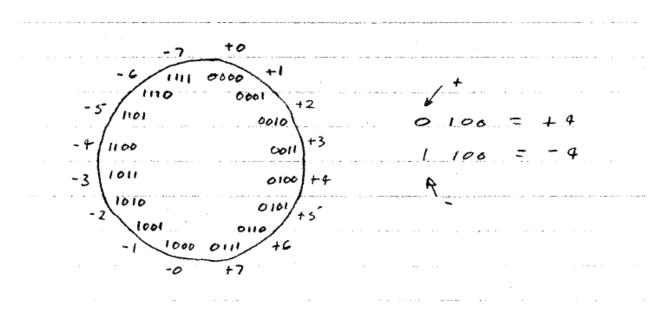

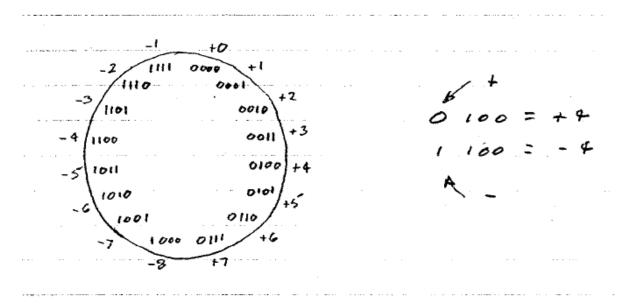

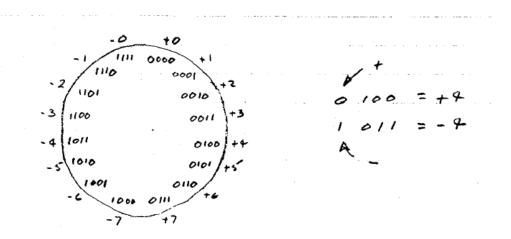

#### **Signed Magnitudes**

In binary notation, an n-bit data word can represent the first 2<sup>n</sup> non-negative integers. To allow for both positive and negative numbers, the most significant bit (MSB) can be designated as the sign bit (0 for positive numbers, 1 for negative numbers). The lower order bits then represent the magnitude of the number in binary notation.

The figure below shoes a "number where" representation of a 4-bit number system. The figure shows the binary numbers and their decimal integer equivalents, assuming that the numbers are interpreted as sign and magnitude.

The largest positive number that can be represented in three data bits is  $+7 = 2^3 - 1$ . Similar the smallest negative number is -7.

This method has the following disadvantages:

- The number zero has two different representations

- Two different arithmetic circuits are required to process positive and negative numbers, see the following straight-binary example giving incorrect answers:

$$e.g. (-5) + (1) = +101 + 0001 = 1110 = -6!$$

(-3)+(-2) = 1011 + 1010 = 0101 = +5!

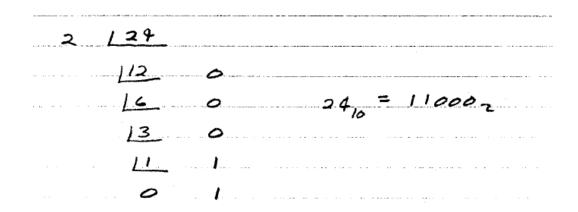

# Complements

A better notation for computers is based on the fact that adding the complement of a number is equivalent to subtracting the number. Hence instead of performing A-B using a subtractor, we can perform A + (-B) to obtain the same result using an adder.

For each base r system, there are two types of complements, namely, the *radix* complement, also known as the r's complement, and the *diminished radix* complement, also known as the (r-1)'s complement.

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

#### **Radix Complement**

The radix complement, denoted by  $[N]_r$ , for a n-digital and r-base number  $(N)_r$  is defined as follows:

$$[N]_{r} = \begin{cases} (r^{n})_{r} - (N)_{r} & \text{for } N \neq 0 \\ 0 & \text{for } N = 0 \end{cases}$$

#### Example:

- A) Obtain the 2-digit 10's complement of 15 and 24.

- B) Represent -15 and -24 in 8-bit signed 2's complement notation.

Answers:

A)  $15_{10} = 10^2 - 15 = 100 - 15 = 85$

$$24_{10} = 10^2 - 24 = 100 - 24 = 76$$

B) In binary:

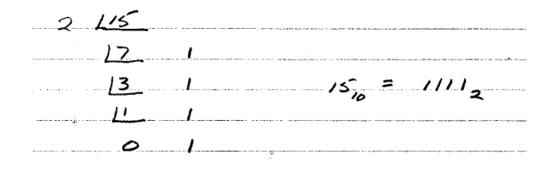

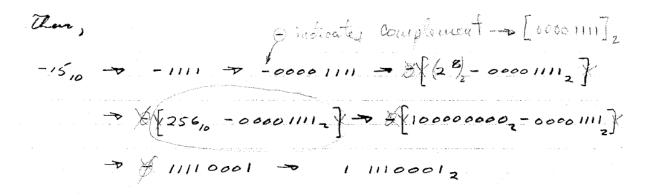

The 2's complement of a binary number can be obtained directly from the given number of copying each bit of the number, starting at the lest significant bit, and proceeding towards the most significant bit until the first 1 has been copied. After the first 1 has been complied, replaced each of the remaining 0's and 1's by 1's and 0's respectively.

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

#### **Example**

The 4-bit 2's complement number representation is shown below. Note there is only one representation for zero.

A) Represent -15 and -24 in 8-bit signed 2's complement notation.

| 2 115    | , | ennen 11a australia eta eta eta eta eta eta artea eta eta artea | ar 1 Main - Main - Main Angelan Proba - Markalainna a' 1. Ia |   |

|----------|---|-----------------------------------------------------------------|--------------------------------------------------------------|---|

| 17       |   |                                                                 | and 1,                                                       |   |

| 13       |   | 15,                                                             | = ////                                                       | 2 |

| <u> </u> |   |                                                                 | -                                                            |   |

| 0        |   |                                                                 |                                                              |   |

Convert 1111 to 8-bit number:

#### 00001111

Starting from left-hand side, invert each bit until the last '1' is encountered:

#### **1111000**<u>1</u>

Therefore -15 is 11110001 in signed 2's complement.

Again convert to 8-bit number:

00011000

Starting from left-hand side, invert each bit until the last '1' is encountered:

## **1110**<u>1</u>000

Therefore -24 is 11101000 in signed 2's complement.

The 4-bit 2's complement number representation is shown below. Note there is only one representation for zero.

# **Two's Complement Arithmetic**

# <u>Addition</u>

Two n-bit signed binary numbers in 2's complement format are added by performing a binary addition of the two numbers, including the sign bits. If a carryover bit results from the leftmost bit, it is discarded. The leftmost bit of the result will give the sign of the sum.

If the sign bit is a 1 we must take the 2's complement of the result to get the real magnitude of the final answer.

#### **Subtraction**

In 2's complement format subtraction of two signed numbers is performed by adding the 2's complement of the subtractand to the numerand. If a carryover results from the leftmost bit, it is discarded. Also the leftmost bit gives the sign of the difference.

Note that the 10's complement can be obtained by forming the 9's complement and adding 1. The 2's complement can be obtained by forming the 1's complement ad adding 1. The 1's complement is formed by changing 1's to 0's and 0's to 1's. The 1's complements representation is shown below. Note the two representations of zero:

#### **Example**

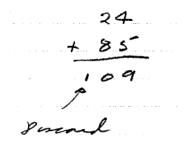

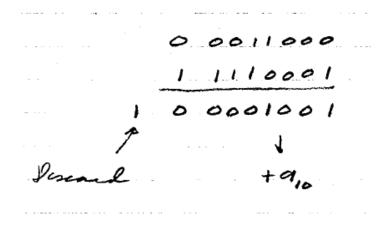

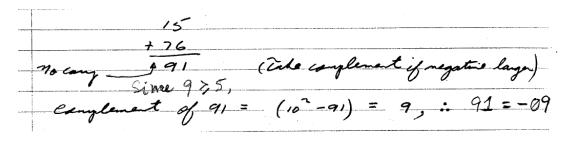

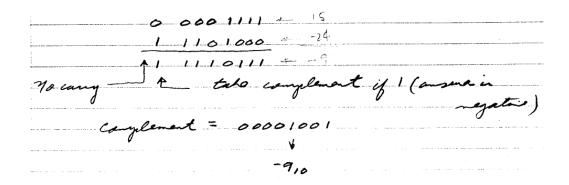

Perform (A) 24-15 and (B) 15-24 directly and by complement notation.

Answers:

A) Direct

| 14. I | 2  | 4 | a |  |

|-------|----|---|---|--|

|       | -/ | 5 | - |  |

|       |    | 9 |   |  |

10's Complement

ECED2200 Digital Circuits Notes - © 2012 Dalhousie University

#### 2's Complement

#### B) Direct

#### 10's Complement

#### 2's complement

Note that for the 10's complement the carryover is discarded and if the result is negative the complement must be taken to get the final result.

# **Binary Coded Decimal**

For convenience, computer input/output devices may accept/provide decimals on the human side and binaries on the computer side. In a binary-coded decimal number each of the decimal digital is coded in binary, using 4 bits. For example in the 8421 code  $6_{10} = 0110_2$ ,  $3_{10} = 011_2$ , and  $363 = 0011\ 0110\ 0011_{BCD}$ .

When a computer is to handle letters as well as numbers, the *alphanumeric* code is used. In the American Standard Code for Information Interchange (ASCII) seven bits are used to represent all the characters and punctuation marks on a teletypewriter keyboard plus some control signals. Note that  $2^7 = 128$ combinations of 7 bits. An eighth bit, the MSB, is a *parity bit* used in error correction. In the *even parity* connection, the MSB is set so that the number of 1's in each ASCII character is even, the present of an odd number of 1's indicates an error.

# **Boolean Algebra**

Boolean algebra is useful in manipulating binary variables (0,1) in OR, AND, or NOT relations and in the analysis and design of all types of digital systems.

#### **Boolean Theorems**

The basic postulates are given in the tables below. In general, the inputs and outputs are variables (either 1 or 0).

#### **Boolean Postulates in 0 and 1**

| OR        | AND      | NOT                |

|-----------|----------|--------------------|

| 0+0=0     | 0.0=0    | $\overline{a} = 1$ |

| 0+1=1     | 0.1=0    | T = 0              |

| 1 + 0 = 1 | 1.0=0    |                    |

| 1+1=1     | 1. 1 = 1 |                    |

|           |          |                    |

### **Basic Boolean Identities**

| No. | Identity                                                                                                                                                                                        | Comments          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1   | A+0=A                                                                                                                                                                                           | Operations with 0 |

|     |                                                                                                                                                                                                 | and 1             |

| 2   | A+1=1                                                                                                                                                                                           | Operations with 0 |

|     |                                                                                                                                                                                                 | and 1             |

| 3   | A+A=A                                                                                                                                                                                           | Idempotent        |

| 4   | $A + \overline{A} = 1$                                                                                                                                                                          | Complements       |

| 5   | A ● 0=0                                                                                                                                                                                         | Operations with 0 |

|     |                                                                                                                                                                                                 | and 1             |

| 6   | A●1=A                                                                                                                                                                                           | Operations with 0 |

|     |                                                                                                                                                                                                 | and 1             |

| 7   | $A \bullet \underline{A} = A$                                                                                                                                                                   | Idempotent        |

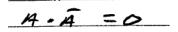

| 8   | $\underline{A} \bullet \overline{A} = A$                                                                                                                                                        | Complements       |

| 9   | Ā=A                                                                                                                                                                                             |                   |

| 10  | A+B=B+A                                                                                                                                                                                         | Commutative       |

| 11  | $A \bullet B = B \bullet A$                                                                                                                                                                     | Commutative       |

| 12  | A+(B+C)=(A+B)+C=A+B+C                                                                                                                                                                           | Associative       |

| 13  | $A \bullet (B \bullet C) = (A \bullet B) \bullet C = A \bullet B \bullet C$                                                                                                                     | Associative       |

| 14  | $A \bullet (B+C) = (A \bullet B) + (A \bullet C)$                                                                                                                                               | Distributive      |

| 15  | $A+(B\bullet C)=(A+B)\bullet(A+C)$                                                                                                                                                              | Distributive      |

| 16  | $A+(A \bullet B)=A$                                                                                                                                                                             | Absorption        |

| 17  | $A \bullet (A+B) = A$                                                                                                                                                                           | Absorption        |

| 18  | $(\mathbf{A} \bullet \mathbf{B}) + (\overline{\mathbf{A}} \bullet \mathbf{C}) + (\mathbf{B} \bullet \mathbf{C}) = (\mathbf{A} \bullet \mathbf{B}) + (\overline{\mathbf{A}} \bullet \mathbf{C})$ | Consensus         |

| 19  | $\overline{A+B+C+}=\overline{A}\bullet\overline{B}\bullet\overline{C}$                                                                                                                          | De Morgan         |

| 20  | $\overline{\mathbf{A} \bullet \mathbf{B} \bullet \mathbf{C} \bullet} = \overline{\mathbf{A}} + \overline{\mathbf{B}} + \overline{\mathbf{C}}$                                                   | De Morgan         |

| 21  | $(A+\overline{B}) \bullet B = A \bullet B$                                                                                                                                                      | Simplification    |

| 22  | $(A \bullet \overline{B}) + B = A + B$                                                                                                                                                          | Simplification    |

The validity of the 22 rules can be verified by substituting all possible values for the Boolean variables and evaluating the left and right-hand sides of each identity. This is known as a proof by *perfect induction*.

#### Example:

Use proof by induction to verify the consensus identity:

| (A       | 1B) | + (Ā | · () + | - (B.C | ) = (P   | +·B)+(A·C | ; )         |

|----------|-----|------|--------|--------|----------|-----------|-------------|

| (*       |     |      |        | ())/() | )        |           |             |

|          |     |      |        |        | <u> </u> | LHS       | RHS         |

| A        | ΒC  | - Ā  | A.B    | Ā·C    | B.C      |           | (A·B)+(A·C) |

| 0        | 00  | > 1  | 0      | 0      | 0        | 0         | 0           |

| 0        | 0 1 | 1    | 0      | 1      | 0        | <u> </u>  | I           |

| 0        | 1 0 | > 1  | 0      | 0      | 0.0      | 0         | 0           |

| 0        | 1.1 |      | 0      | 1.     | 1        | . I       | I           |

|          | 0 0 |      | 0      | 0      | 0        | 0         |             |

|          | 0 1 | 0    | 0      | 0      | 0        | 0         | 0           |

| <u> </u> | 1 0 | 0    |        | 0      | 0        | 1         | 1           |

|          |     | 0    |        | 0      | . 1      | 1         |             |

Note that when  $B \bullet C=1$ , this means B=C=1. One of the remaining terms will always be 1 in that case, which is why  $B \bullet C$  is redundant.

The first nine identities are the fundamental relations of Boolean algebra. Identities 10-14 are similar to the laws of ordinary algebra. Identities 10 and 11 are the commutative rules, 12 and 13 are the associative rules, and 14 and 16 are the distributive rules. Identities 16-18 do not apply to ordinary algebra but are very useful in Boolean Algebra. Identities 16 and 17 are the absorption identities; identity 18 is the consensus identity; identity 19 and 20 are De Morgan's rules. Formally identities 21 and 22 are simplification rules.

The basic identities can be used to simplify Boolean functions.

#### **Example**

Derive the absorption rule:

$A + (A \cdot B) = A$ Using other basic theorems. A + (A.B) = (A+A) · (A+B) using identity = A. (A+B) using 3 = A.A + A.B using 14 USANG >= A.I + A.B using 6 and 7 = A. (1+B) using 14 = A.1 usig 2 = A 6

#### **De Morgan's Theorems**

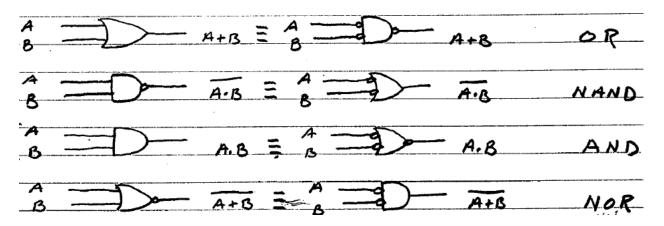

De Morgan's theorems are easily interpreted in terms of logic circuits. The first says that a NOR gate is equivalent to an AND gate with NOT circuits in the inputs. The second says that a NAND gate is equivalent to an OR gate with NOT circuits in the inputs. As started by Shannon, De Morgan's theorem says:

To obtain the inverse of any Boolean function, invert all variables and replace all OR's by AND's and all AND's by OR's.

#### <u>Example</u>

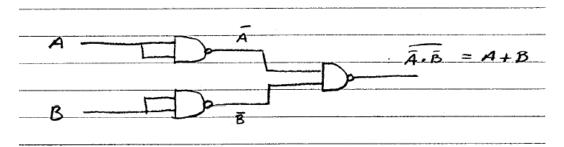

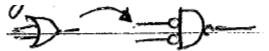

Use De Morgan's theorems to design a combination of NAND gates equivalent to a two-input OR gate.

The desired function is:

f = A + B

Using De Morgan's theorem (Identity 19) we get:

$$f = A + B = \overline{\overline{A} \cdot \overline{B}}$$

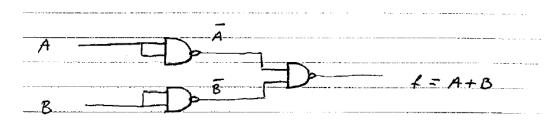

Suggesting a NAND gate with NOT inputs because  $\overrightarrow{A.A} = \overrightarrow{A}$  by theorem 7, a NAND gate with the inputs tied together performs the NOT operation. The logic circuit is shown below:

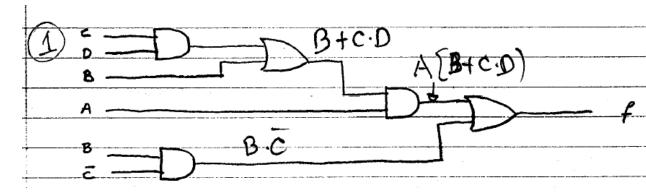

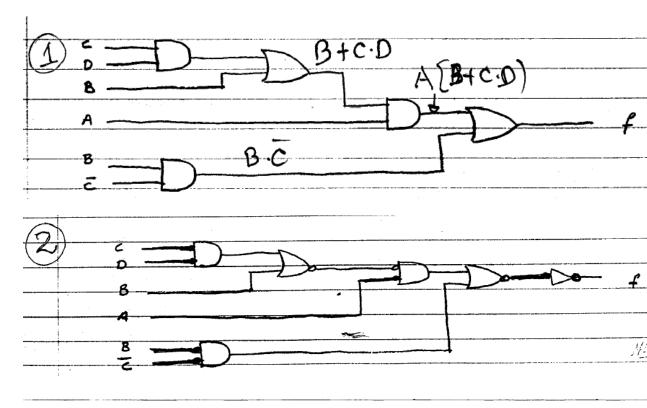

#### **Logic Circuit Analysis**

The Boolean identities permit us to manipulate logic statements or functions directly, without setting up truth tables. Also, the use of Boolean algebra can lead to simpler logic statements that are easier to implement. De Morgans theorems are useful in finding NAND operations that are equivalent to other operations.

The analysis of a logic circuit consists in writing a logic statement expression the overall operation of the circuit. This can be done by starting at the input and tracking through the circuit noting the function realized at each output. The resulting expressions can be simplified or put into an alternate form by using Boolean Algebra. A truth table can be constructed.

Note the symbol  $A \bullet B$  can be simplified to AB or A(B).

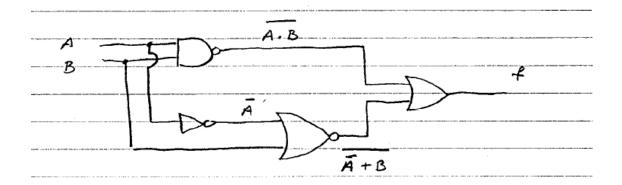

#### **Example**

Analyze the given logic circuit:

Construct the truth table to demonstrate that this circuit could be replaced by a single NAND gate.

The suboutputs are as noted on the diagram. The overall function can be simplified as follows:

$f = \overline{A \cdot B} + \overline{A} + B$ = (A+B) + A.B using 19al 20 = A + (1+A). B using 14 = Ā + 1.B ung 2 = Ā+B uning G = A.B using 20

The truth table is given below:

| AB  | A.B | A.B | Ā+B | Â+B | f        |

|-----|-----|-----|-----|-----|----------|

| 0 0 | 0   |     | 1   | 0   | <u> </u> |

| 0_1 | 0   |     | /   | 0   | 1        |

| 10  | 0   |     | 0   |     | <u> </u> |

| 11. |     | 0   | /   | 0   | 0        |

|     |     |     |     |     |          |

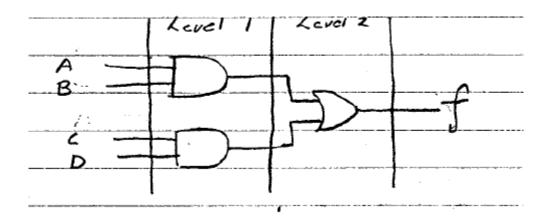

# **Two-Level Combinational Logic**

A two-level implementation means that there are only two gates between input and output. A two-level implementation of  $f = A \bullet B + C \bullet D$  is shown below:

Each appearance of a variable or its complement is an expression is called a *literal. Combinational* networks are those where the outputs depend only on the current input. They are circuits without a memory.

# **Logic Circuit Synthesis**

The logic designer starts with a logic statement or truth table, converts the logic function into a convenient form and then realizes the desired functions by means of a standard or special logic Elements.

# Adding

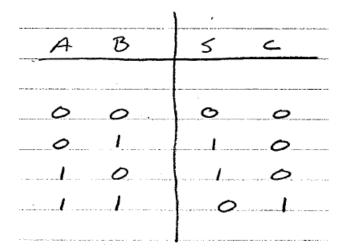

# The Half Adder

Consider the process of addition. In adding two binary digits, the possible sums are shown below. Note that when A=1 and B=1, the sum in the first column is 0 and there is a carry of 1 to the next higher column.

| A     |     |     |

|-------|-----|-----|

| A =   | 1   | 00  |

| + B = | 10  | 10  |

|       | 0.1 | 1.0 |

As indicated in the truth table, the half-adder must perform as follows: "s is 1 if A is 0 AND B is 1, OR if A is 1 AND B is 0; c is 1 if A AND B are 1". In logic nomenclature, this becomes:

Which can be written as:

Note that a full-adder can accept the carry from the adjacent column.

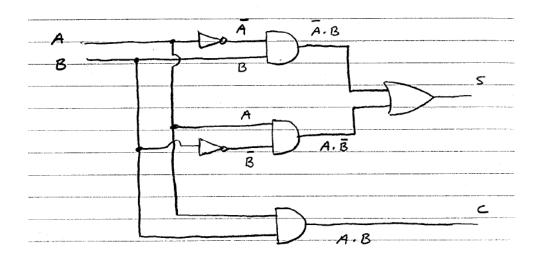

To synthesize a half-adder circuit, start with the output and work backwards. The above equation indicates that the sum s is the output of an OR gate; the inputs are obtained from AND gates; inversion of A and B is necessary. The above expression also indicates that the carry c is the output of an AND gate. The logic circuit is shown below.

Different Boolean expressional are possible for a given logic statement and some will lead to better circuit realizations than others. Consider the last expression:

$$\overline{A} \cdot \overline{B} + \overline{A} \cdot \overline{B} = \overline{A} + \overline{B} + \overline{A} + \overline{B} \qquad \text{using 19}$$

$$= (\overline{A} + \overline{B}) \cdot (\overline{A} + \overline{B}) \qquad \text{using 20}$$

$$= (\overline{A} \cdot \overline{A}) + (\overline{A} \cdot \overline{B}) + (\overline{A} \cdot \overline{B}) + (\overline{B} \cdot \overline{B}) \qquad \text{using 14}$$

$$= (\overline{A} \cdot \overline{B}) + (\overline{A} \cdot \overline{B}) \qquad \text{using 8}$$

$$= (\overline{A} + \overline{B}) + (\overline{A} + \overline{B}) \qquad \text{using 19}$$

$$= (\overline{A} + \overline{B}) \cdot (\overline{A} + \overline{B}) \qquad \text{using 20}$$

$$= (\overline{A} + \overline{B}) \cdot (\overline{A} + \overline{B}) \qquad \text{using 20}$$

$$= (\overline{A} + \overline{B}) \cdot (\overline{A} + \overline{B}) \qquad \text{using 20}$$

And referring to the truth table we see that another interpretation is:

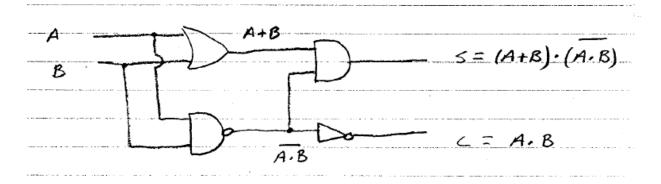

"S is 1 if (A OR B) is 1 AND (A AND B) is NOT 1". The binary addition is:

$$5 = (A + B) \cdot (\overline{A \cdot B})$$

and  $c = A \cdot B$

The synthesis of the circuit, working backwards from the output, is shown below:

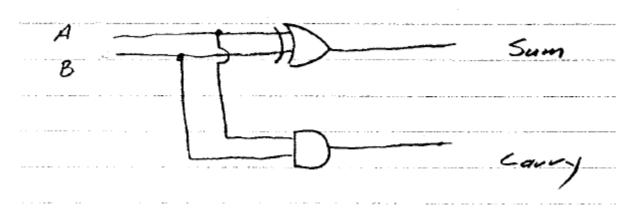

The circuit is better than the previous one in that fewer logic elements are used and the longest path from input to output passes through fewer levels. In terms of the Exclusive-OR gate, the half-adder takes the simple form shown below:

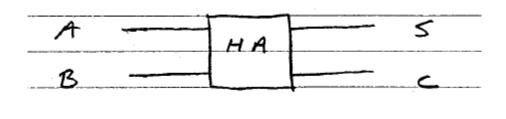

The half adder can be treated as a discreet logic element and represented as shown below:

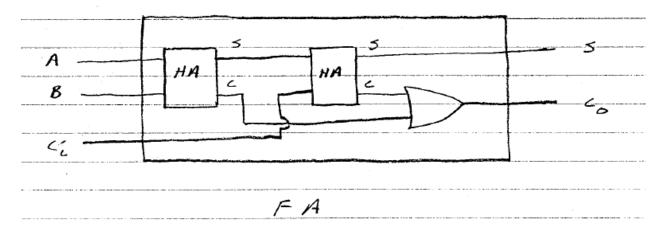

# **The Full Adder**

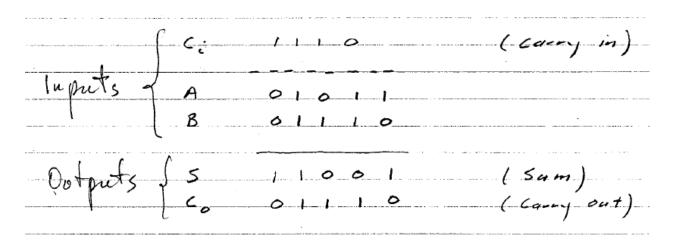

To add two binary digits (bits) the half-adder performs the most elementary part. For a complete addition we need a fill-adder capable of handling the carry input as well. The addition process is illustrated below where ci is the carry from the proceeding column:

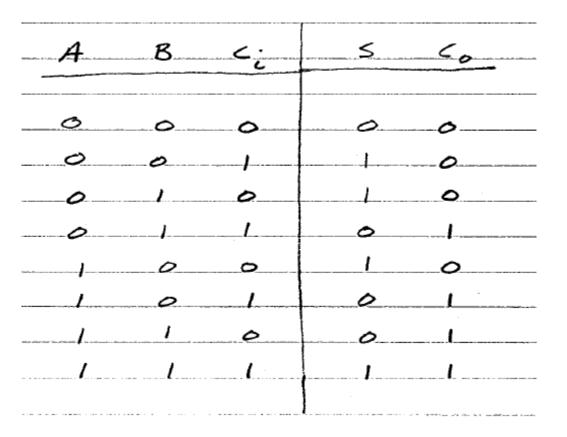

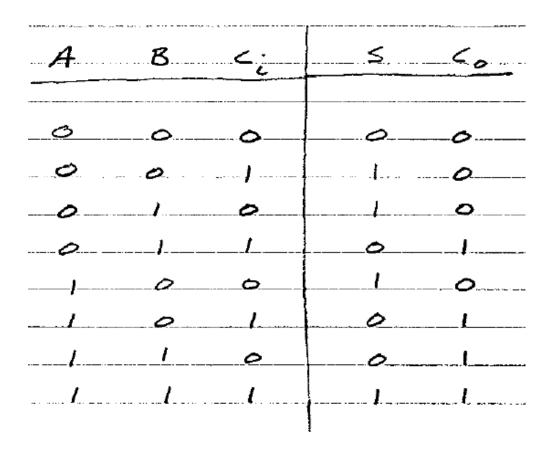

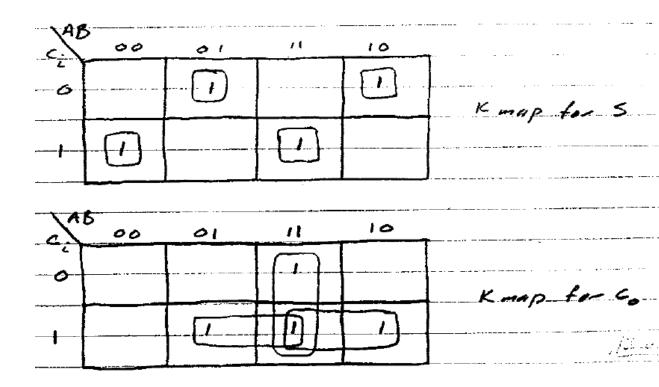

Each carry of 1 must be added to the two digits in the next column, so the logic circuit must be able to combine three inputs. The truth table for the full-adder is shown below.

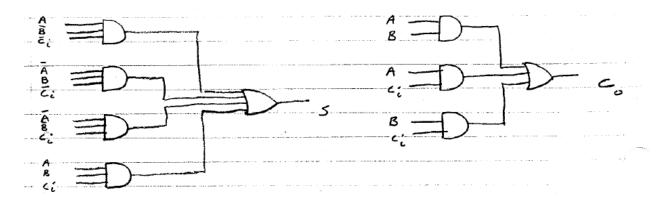

Note that both S and Co have four cases with 1's in the output columns. In logic notation we have:

$$S_{is} ONE W low ... S = A \cdot \overline{B} \cdot \overline{C_{i}} + \overline{A} \cdot \overline{B} \cdot \overline{C_{i}} + \overline{A} \cdot \overline{B} \cdot \underline{C_{i}} + A \cdot \underline{B} \cdot$$

The expression for Co can be simplified as follows:

$$\begin{aligned} \mathcal{L}_{0} &= \overline{A} \cdot \overline{B} \cdot \mathcal{L}_{i} + A \cdot \overline{B} \cdot \mathcal{L}_{i} + A \cdot \overline{B} \cdot \overline{\mathcal{L}}_{i} + A \cdot \overline{B} \cdot \mathcal{L}_{i} \\ &= \overline{A} \cdot \overline{B} \cdot \mathcal{L}_{i} + A \cdot \overline{B} \cdot \mathcal{L}_{i} + A \cdot \overline{B} \cdot \overline{\mathcal{L}}_{i} + A \cdot \overline{B} \cdot \mathcal{L}_{i} + A \cdot \overline{B} \cdot \mathcal{$$

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

Although this leads to a simpler expression, applying the rules of Boolean algebra in this situation does not guarantee the simplest expression. A more systematic approach will be discussed later.

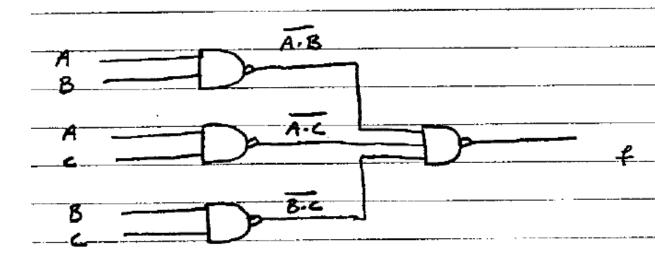

Using the expression for S and Co the full adder can be implemented as shown below:

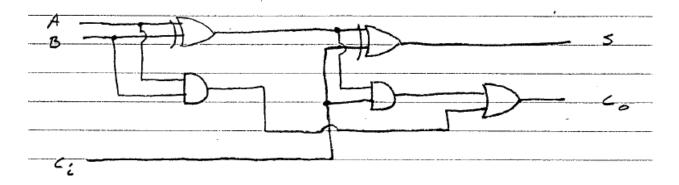

The full adder can also be implanted with two half-adders and one OR gate, as shown below:

For this case the S output from the second half-adder is the Exclusive-OR of Ci and the output of the first half-adder, giving:

$$S = c_{i} \oplus (A \oplus B)$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot (\overline{A} \cdot B + A \cdot \overline{B})$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot ((\overline{A} \cdot B) \cdot (\overline{A} \cdot \overline{B})) \xrightarrow{\text{min}} 19$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot ((A + \overline{B}) \cdot (\overline{A} + B)) \xrightarrow{\text{min}} 20$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot ((A + \overline{A} + A \cdot B + \overline{B} \cdot \overline{A} + \overline{B} \cdot B))$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot (A \cdot \overline{A} + A \cdot B + \overline{B} \cdot \overline{A} + \overline{B} \cdot B)$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot (A \cdot \overline{A} + A \cdot B + \overline{B} \cdot \overline{A} + \overline{B} \cdot \overline{B})$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot (A \cdot B + \overline{A} \cdot \overline{B})$$

$$= \overline{c_{i}} (\overline{A} \cdot B + A \cdot \overline{B}) + c_{i} \cdot (A \cdot B + \overline{A} \cdot \overline{B})$$

as before. The carry out is the (Exclusive-OR of A and B AND Ci) OR'ed with A AND B, or:

$$C_{o} = c_{i} \cdot (\bar{A} \cdot B + A \cdot \bar{B}) + A \cdot B$$

$$= \bar{A} \cdot B \cdot c_{i} + A \cdot \bar{B} \cdot c_{i} + A \cdot B$$

$$= \bar{A} \cdot B \cdot c_{i} + A \cdot \bar{B} \cdot c_{i} + A \cdot B \cdot (\bar{c}_{i} + c_{i}) - \frac{g_{i}}{g_{i}}$$

$$= c_{o} = \bar{A} \cdot B \cdot c_{i} + A \cdot \bar{B} \cdot c_{i} + A \cdot \bar{B} \cdot c_{i} + A \cdot B \cdot c_{i}$$

as before.

The full adder can be treated as a discreet logic element and represent as shown below:

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

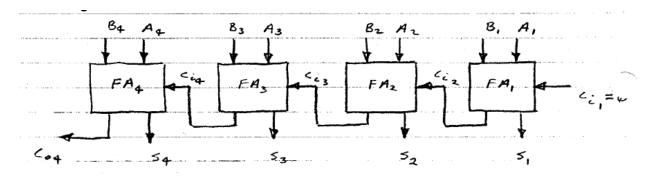

To obtain the binary addition of two n-bit binary numbers, we cascade n fulladder circuits together, with the carry in of a full-adder being connected to the carry out of the previous full adder. The interconnection of four full-adders to provide the addition of two 4-bit binary numbers is shown below:

Note that the initial adder need only be a half-adder since the initial Ci is 0.

MSI (Medium Scale Integration) packages are available that contain 4 and 8-bit binary adders.

#### **Subtraction**

# **Direct Approach**

Subtraction can be implemented with logic circuits in a direct manner as was done for adders. In this method the subtractend is subtracted from the numerend to form the difference. If the numerend is smaller than the subtractend, a 1 is borrowed from the next significant position. This borrow must be conveyed to the next stage. As in the case of adders, there are half- and full-subtractors.

ECED2200 Digital Circuits Notes - © 2012 Dalhousie University

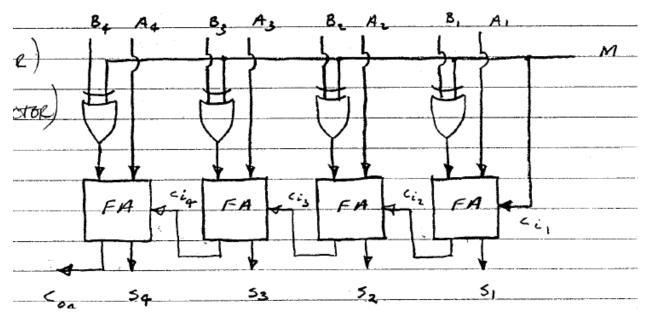

# **Indirect Approach (Using Adders)**

As discussed earlier, subtraction may be accomplished by taking the complement of the subtractend and adding it to the numerend. Subtraction then becomes addition requiring full-adders for machine implementation. The addition and subtraction operation can be combined into one circuit with the common binary adder. This is done by including an Exclusive-OR gate with each full adder as shown below. The mode input (M) controls the operation. When M=0, the circuits is an adder, and when M=1, the circuit becomes a subtractor. Each Exclusive-OR gate has input M and one of the inputs of B (Bi).

When M=0, we have Bi XOR 0 = Bi. The full-adders receive the value Bi, the input carry is 0, and the circuit performs A+B. When M-1, we have Bi XOR 1 = NOT Bi, and the input carry is 1. The Bi inputs are all complemented and a 1 is added through the input carry. The circuit performs (A + NOT(B) + 1) which is A plus the 2's complements of B. Note that NOT(B) is actually the 1's complement, but also called the "diminished 2's complement".

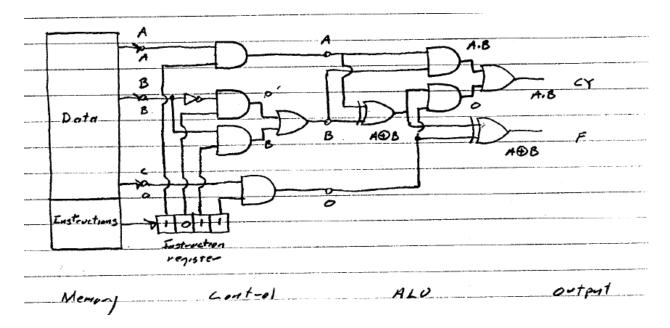

# Arithmetic Logic Unit (ALU)

A arithmetic logic unit (ALU) is a combinational network of logic gates arranged to perform addition, complementing, incrementing, and the associated register for temporary storage of data or results. The ALU is governed by a control unit, which sets the various logic gates, feeds the numeric data, and provides the clock pulse

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

that regulates the speed of operation. An ALU and its control unit for an elementary example are shown below.

In this case the stored number A and B are operated according to the instruction in the form of a 4-bit word. The instruction is taken from memory and placed in a register. The instruction 1011 shown sets the logic gates so that A, B, and O are available for processing. Other instructions and the outputs are shown in the table below. There are  $2^4 = 2 \times 32$  possibilities.

| c.       | Instruction | Enpart to<br>ALU | Foutput of ALU      | Cy output of 460 |

|----------|-------------|------------------|---------------------|------------------|

| 0        | 1011        | A, B, O          | ABB                 | A.B              |

| 0        | 1110        | A,1,0            | A (comp. of M)      | A                |

| 0        | 1010        | -                | AGB                 | A.B              |

| 1        | 1101        | A, 8,1           | ABE                 | (ADB)+A.B = ADB  |

| <u> </u> | 0101        | 0,8,1            | B+1 = 2's comp of B | Ē                |

|          | 1011        |                  | ADB                 | A.B+ABB = A+B    |

|          |             |                  |                     |                  |

# <u>A Design Procedure</u>

In logic design, gates must be combined to realize the desired function. The design proceeds according to the following steps.

ECED2200 Digital Circuits Notes - © 2012 Dalhousie University

- 1. Statement of function

- 2. Form a truth table

- 3. Obtain the Boolean expression of the function

- 4. Manipulate the Boolean expression to the simplest form

- 5. Realize in terms of AND, OR and NOT gates

#### **Example**

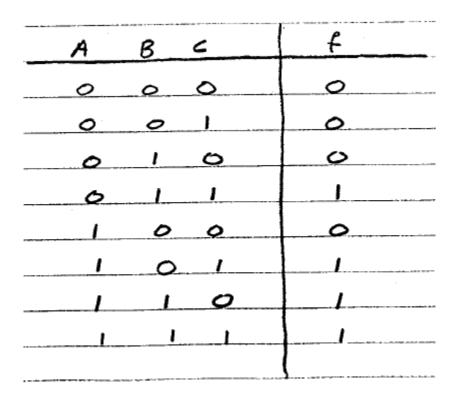

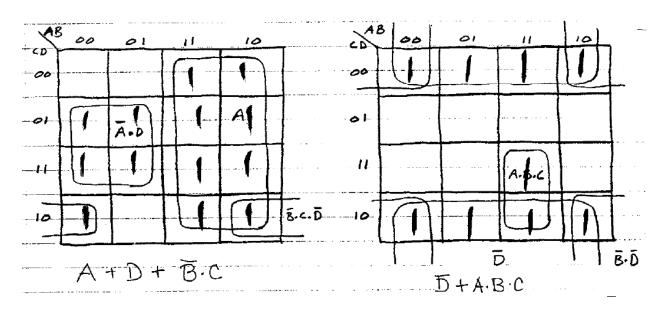

For increased reliability on a spacecraft triple sensing systems are used; no action is taken unless at least two of those systems call for action. The required system is known as a vote taker whose truth table is shown below:

Because the function is YES(1) only when a majority of inputs are YES, the Boolean expression is:

$f = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$

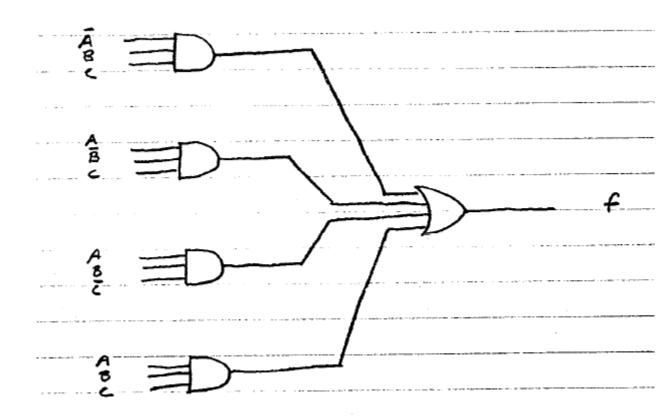

If the complement of each variable is available (true in most computers), the realization is a combination of four AND gates feeding an OR gate:

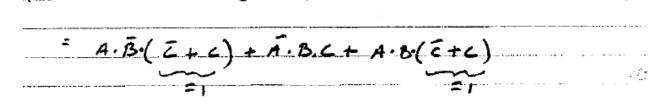

If the complements are not available eight logic elements (three NOT elements) would be required, and simplification of the circuit is desirable. We proceed as follows:

1 = A.B.C + A.B.C + A.B.E + A.B.L + A.B.C Hilu  $= A.B.(\varepsilon + c) + c.(A.B + A.\overline{B} + \overline{A}.B)$

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

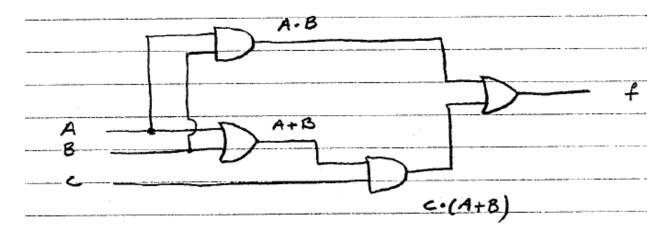

$= A.B + c. \left[ A.(B+\overline{B}) + \overline{A}.B \right]$ = A.B + C. (A+A.B) = A, B + c. [(A+A).(A+B)] using 15 =  $A.B + c \cdot (A+B)$

This function requires only four logic elements as shown below:

# **Two-Level Canonical Forms**

A Boolean function can be written in different forms. Certain forms, however, lead to more desirable combinational networks. These forms which are *canonical* forms are of two types: sum of products and product of sums.

## **Sum of Products**

We have used the sum of products form in our earlier work. A sum of products expression is formed as follows. Each row of the truth table in which the function takes on the value 1 contributes an ANDed term. These are called *minterms*. A minterm is defined as an ANDed product of literals in which each variable appears exactly once in either normal or complemented form, but not both. The minterms are then ORed to form the expression for the function. The minterm expression is equivalent since it is derived from the truth table.

The figure below shows a truth table for an arbitrary function f and its complement. The minterms and maxterms for each row are also shown. The minterm expressions for f and f NOT are:

$f = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot \overline{C} + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C$  $\vec{F} = \vec{A} \cdot \vec{B} \cdot \vec{C} + \vec{A} \cdot \vec{B} \cdot \vec{C} + \vec{A} \cdot \vec{B} \cdot \vec{C}$

Truth table which above is based on:

| A        | B        | c         | 4        | Ŧ        | Minterns     | Maxte-ms                                  |

|----------|----------|-----------|----------|----------|--------------|-------------------------------------------|

| 0        | 0        | 0         | 0        | 1        | Ā. Ē. Ē = m, | A+B+C = Mo                                |

| 0        | 0        | i         | 0        | <u> </u> | A. B.C = M,  | A+B+E = M1                                |

| e        |          | <u>_o</u> | 0        | 1        | A. B.E = m2  | AtB+G = M2                                |

| 0        |          |           | <u> </u> | 0        | A.B.C = #13  | At&ré = N3                                |

| (        | <u> </u> | 0         | <u> </u> | 0        | A. 8.2 = m   | A+B+C = Me                                |

|          | 0        | <b>t</b>  | L        | 0        | A.B.C = "5   | A+B+E = Ms-                               |

| 1        | <u> </u> | 0         | ļ        | 0        | A. 8.2 = mc  | $\overline{A} + \overline{B} + C = M_{G}$ |

| 1        | L        | <b>I</b>  |          |          |              | A+B+E = NIZ                               |

| <u>_</u> |          |           | L        |          |              |                                           |

The above expression can be written in a shorthand notation. Note that the indexing of the Boolean variables is important in deriving the minterm and maxterm. In shorthand notation we have:

$f(A,B,C) = \Xi m_i(3,4,5,6,7) = m_3 + m_4 + m_5 + m_6 + m_7$   $\bar{f}(A,B,C) = \Xi m_i(0,1,2) = m_0 + m_1 + m_2$

Where  $\leq m_i$  ( — ) means the sum of all the minterms whose subscript *i* is given inside the parentheses.

The minterm expression is not likely to be the simplest form of the function. The expression for f can be reduced by using Boolean algebra.

f = A.B.C + A.B. C + A.B.C + A.B. C + A.B.C

The minimized gate-level implementation of *f* is shown below:

The expression *f* NOT can also be reduced:

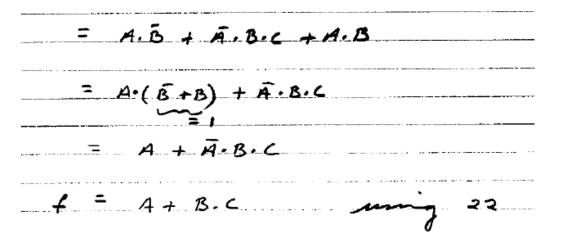

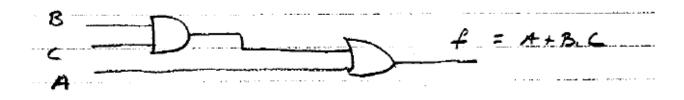

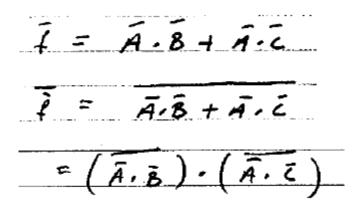

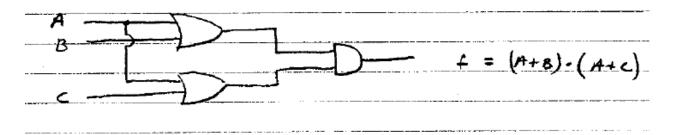

I= A.B.C + A.B.C + A.B.C  $= \overline{A} \cdot \overline{B} \cdot (\overline{z} + c) + \overline{A} \cdot \overline{B} \cdot \overline{c}$   $= \overline{A} \cdot \overline{B} + \overline{A} \cdot \overline{B} \cdot \overline{c}$ ----- $\overline{A} \cdot (\overline{B} + B \cdot \overline{c})$ = A. (B+E) nmg 22 =  $\overline{A} \cdot \overline{B} + \overline{A} \cdot \overline{C}$

ECED2200 Digital Circuits Notes – © 2012 Dalhousie University

## **Product of Sums**

A product of sums expressions is formed as follows. Each row of the truth table in which the function takes on the value 0 contributes an ORed therm. These are called *maxterms*. A maxterm is defined as an ORed sum of literals in which each variable appears exactly once in either true or completed form, but not both. The maxterms are then ANDed to form the expression for the function. This is opposite to the way we formed minterms.

The products of sum of functions *f* and *f NOT* is obtained from the truth table as:

$f = (A + B + c) \cdot (A + B + \bar{c}) \cdot (A + \bar{B} + c)$  $\widehat{I} = (A + \overline{B} + \overline{c}) \cdot (\overline{A} + B + c) \cdot (\overline{A} + B + \overline{c}) \cdot (\overline{A} + \overline{B} + \overline{c}) \cdot (\overline{A} + \overline{B} + \overline{c})$ Using a shorthand notation we can write f and f NOT as:  $f(A,B,C) = TTM_i(a,1,2) = M_a \cdot M_1 \cdot M_2$ F (A, B, C) = T M; (3, 9, 5, 6, 7) = H, M. M. M. M.

Where  $-\pi M_i(-)$  means the product of all the maxterms whose subscript *I* is given inside the parentheses.

# **Conversion Between Canonical Forms**

One canonical form can be mapped into the other by applying De Morgan's Theorem. For example if we apply DeMorgan's Theorem to the minterm expansion of f NOT we get:

$$\vec{f} = \vec{A} \cdot \vec{B} \cdot \vec{c} + \vec{A} \cdot \vec{B} \cdot \vec{c} + \vec{A} \cdot \vec{B} \cdot \vec{c}$$

$$\vec{f} = \vec{A} \cdot \vec{B} \cdot \vec{c} + \vec{A} \cdot \vec{B} \cdot \vec{c} + \vec{A} \cdot \vec{B} \cdot \vec{c}$$

$$= \left(\vec{A} \cdot \vec{B} \cdot \vec{c}\right) \cdot \left(\vec{A} \cdot \vec{B} \cdot \vec{c}\right) \cdot \left(\vec{A} \cdot \vec{B} \cdot \vec{c}\right) + \frac{mmm}{2} \cdot mmm + 19$$

Or:

$$\vec{f} = \left(A + B + c\right) \cdot \left(A + B + \vec{c}\right) \cdot \left(A + \vec{B} + c\right)$$

Which is the maxterm expansion of f. Similarly applying DeMorgan's Theorem to them maxterm expansion of f NOT gives:

$$\overline{I} = (A + \overline{B} + \overline{c}) \cdot (\overline{A} + B + c) \cdot (\overline{A} + B + \overline{c}) \cdot (\overline{A} + \overline{B} + c) \cdot (\overline{A} + \overline{B} + \overline{c})$$

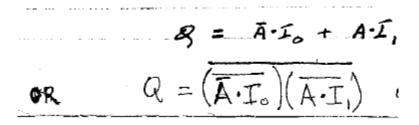

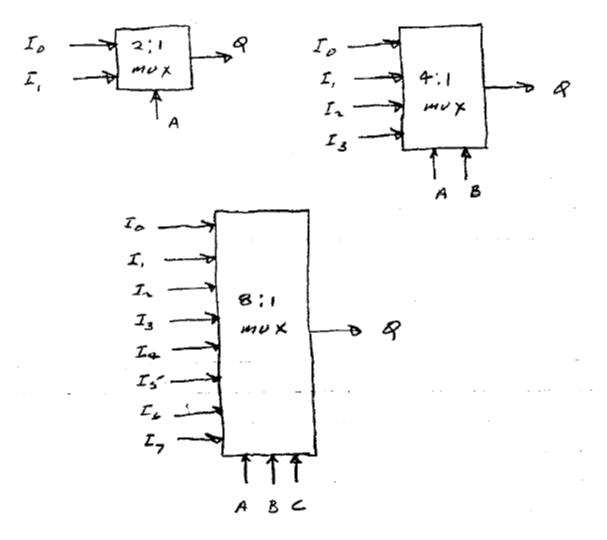

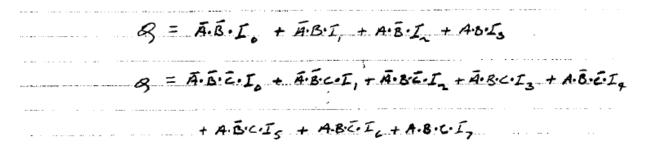

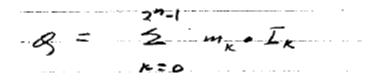

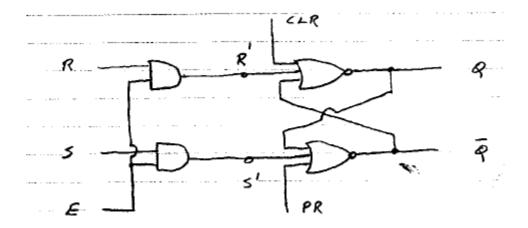

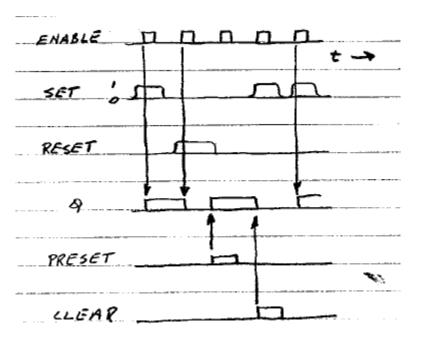

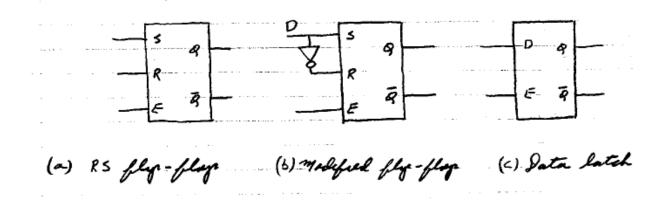

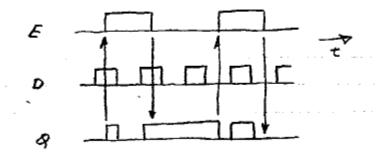

$$\overline{I} = (\overline{A + \overline{B} + \overline{c}}) \cdot (\overline{A} + B + c) \cdot (\overline{A} + B + \overline{c}) \cdot (\overline{A} + \overline{B} + c) \cdot (\overline{A} + \overline{B} + \overline{c})$$